Intel® Quartus® Prime Pro Edition User Guide: Design Optimization

A newer version of this document is available. Customers should click here to go to the newest version.

7. Analyzing and Optimizing the Design Floorplan

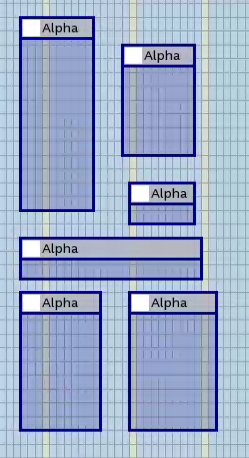

By default, the Compiler determines the best location for logic placement based on your design characteristics and project settings and constraints. You can use the Intel® Quartus® Prime Chip Planner to visualize the available device resources, and then use a variety of constraints to implement specific placement for important logic, and to group blocks together within specific device regions.

For example, you can define a Logic Lock placement constraint to assign design logic to any arbitrary region of physical resources on the target device that you define. When you assign nodes or entities to the Logic Lock region, the Compiler always places that logic inside the region during fitting. You can define the Logic Lock region's size and location.

Section Content

Design Floorplan Analysis in Chip Planner

Defining Logic Lock Placement Constraints

Defining Virtual Pins

Using Logic Lock Regions in Combination with Design Partitions

Creating Clock Region Assignments in Chip Planner

Scripting Support

Analyzing and Optimizing the Design Floorplan Revision History