Intel® Quartus® Prime Pro Edition User Guide: Design Compilation

ID

683236

Date

12/04/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

2.1. Compilation Overview

2.2. Using the Compilation Dashboard

2.3. Design Netlist Infrastructure

2.4. Using the Node Finder

2.5. Analysis & Elaboration Flow

2.6. Design Synthesis

2.7. Design Place and Route

2.8. Incremental Optimization Flow

2.9. Fast Forward Compilation Flow

2.10. Full Compilation Flow

2.11. Compilation Monitoring Mode

2.12. Exporting Compilation Results

2.13. Integrating Other EDA Tools

2.14. Compiler Optimization Techniques

2.15. Synthesis Language Support

2.16. Synthesis Settings Reference

2.17. Fitter Settings Reference

2.18. Design Compilation Revision History

2.6.3.1. Registering the SDC-on-RTL SDC File

2.6.3.2. Applying the SDC-on-RTL Constraints

2.6.3.3. Inspecting SDC-on-RTL Constraints

2.6.3.4. Creating Constraints in SDC-on-RTL SDC Files

2.6.3.5. Using Entity-Based SDC-on-RTL Constraints

2.6.3.6. Types of SDC Files Used in the Intel® Quartus® Prime Software

2.6.3.7. Example: Using SDC-on-RTL Features

2.12.1. Exporting a Version-Compatible Compilation Database

2.12.2. Importing a Version-Compatible Compilation Database

2.12.3. Creating a Design Partition

2.12.4. Exporting a Design Partition

2.12.5. Reusing a Design Partition

2.12.6. Viewing Quartus Database File Information

2.12.7. Clearing Compilation Results

3.1. Factors Affecting Compilation Results

3.2. Strategies to Reduce the Overall Compilation Time

3.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

3.4. Reducing Placement Time

3.5. Reducing Routing Time

3.6. Reducing Static Timing Analysis Time

3.7. Setting Process Priority

3.8. Reducing Compilation Time Revision History

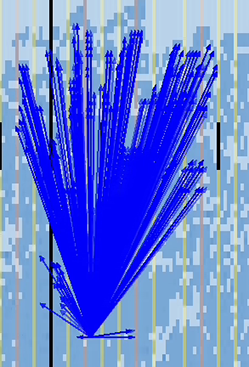

2.8.2.1.3. Analyzing High Fan-out Nets with Snapshot Viewer

- To run the Place or Route stage of the Fitter, double-click the stage in the Compilation Dashboard.

- After the stage completes, click the Snapshot Viewer icon for that stage in the Compilation Dashboard. The Snapshot Viewer opens.

- Under Analyze High Fanout Nets, click Show High Fanout Nets in the Schematic. The path displays and highlights in Tech Map Viewer for further analysis.

- Under Analyze High Fanout Nets, click Show High Fanout Nets in the Chip View. The path displays and highlights in the Chip Planner for further analysis.

Figure 96. Non-Global High Fan-Out Signal in Chip Planner