Advantages of Partial Reconfiguration

Scope of This Document

Prerequisites for Using This Document

Partial Reconfiguration Tools and Methods

Arria 10 SoC Partial Reconfiguration Workflow

Partial Reconfiguration Limitations

Creating the PR Example Design

Generating the Example Software Image

Loading Partial Reconfiguration Designs Using Linux

Important Partial Reconfiguration Terminology

Revision History

Qsys Partial Reconfiguration Freeze Logic

Importing the GHRD Project

Add a Partial Reconfiguration Region to the GHRD

Building the Base Revision with the Reconfigurable Design Partition

Synthesizing an Alternate Persona

Implementing the Alternate Persona

Generating the RBF FPGA Image Files

Design Handoff to Software Developer

Synthesizing an Alternate Persona

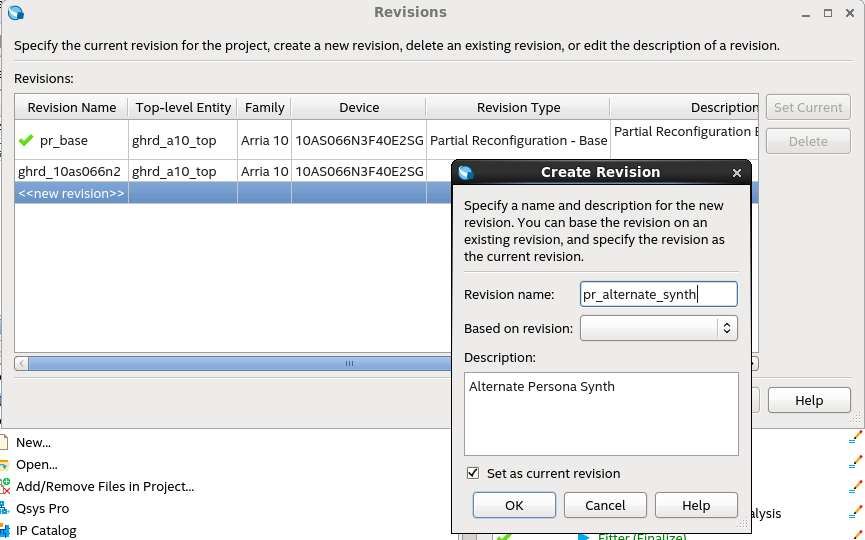

- Create a new design revision for the alternate persona synthesis step. This revision is not based on any existing revision and is created blank with no existing files, settings, or constraints. This revision is only for synthesizing the PR region logic and does not require any of the normal top level settings or constraints, such as pin placement.

Figure 26. Creating Blank Revision for Alternate Persona

Click OK to create the revision and open it as the current revision.

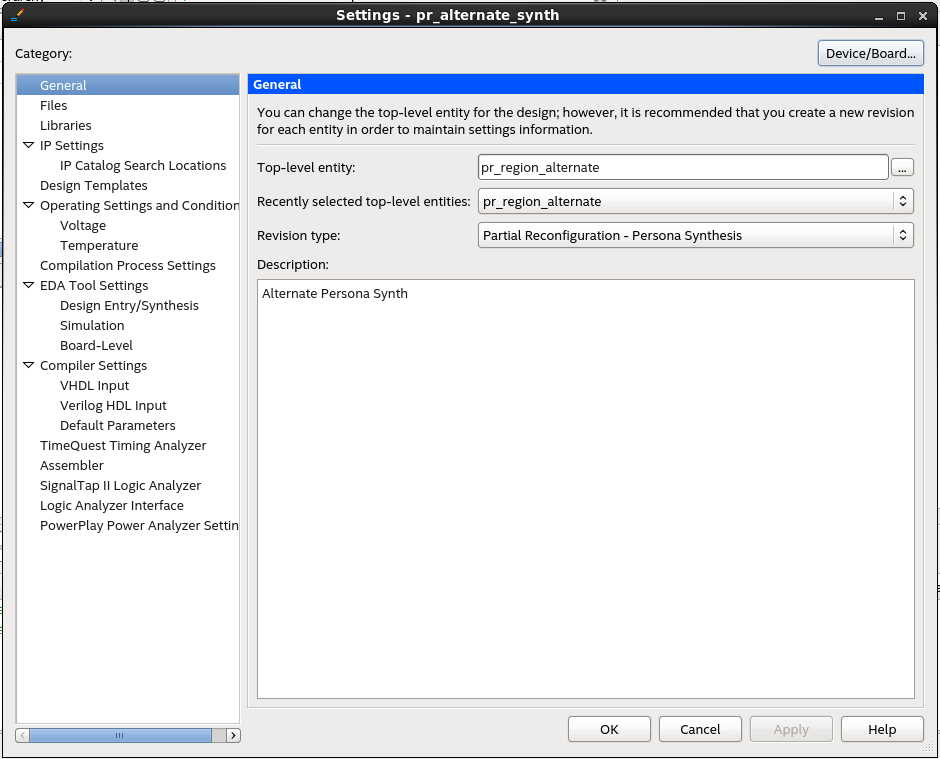

- Ensure that the new revision's Device Type setting matches the other revisions. If it does not, you can change it by clicking Device in the Assignments menu, to open the Device dialog box.

- To change the revision type of the new revision, point to Assignments, click Settings, choose the General category, and change the Revision Type field to Partial Reconfiguration – Persona Synthesis as shown below.

Figure 27. Setting the Revision Type

- Change the Top-level entity field to pr_region_alternate. This is the name of a new Qsys design that is generated in a later step.

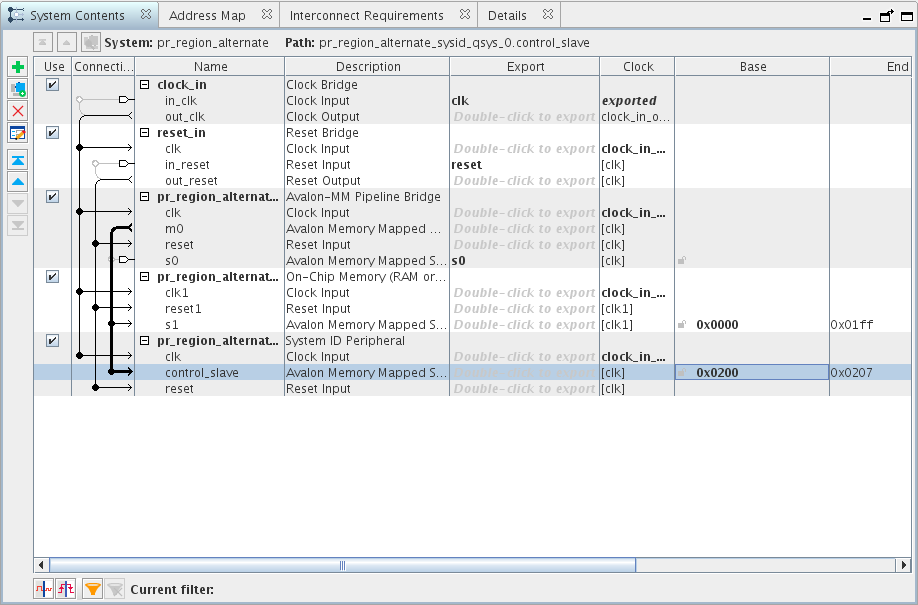

- Create a new Qsys Pro design called pr_region_alternate.qsys as shown below.

Figure 28. New Design for Alternate Persona

- Add an Avalon-MM pipeline bridge, an on-chip memory, and a system ID peripheral, as described in "Creating the Partial Reconfiguration Design". However, configure a different value in the 32-bit system ID field of the system ID peripheral, and set the base address of the system ID peripheral to 0x0200. Leave the on-chip memory base address at 0x0000.

At runtime, software will read the system ID from each design revision. For each PR region, it will read a unique value from a unique address. This will demonstrate that the PR region has changed and Linux was updated properly.

- Click Generate RTL and then Finish. This closes the Qsys Pro design.

- Run the first two stages of the compilation flow (IP generation and analysis and synthesis), as follows:

- If the Compilation Dashboard is not visible, click Compilation Dashboard in the Tasks window.

- Click IP Generation.

- When IP generation is complete, click Analysis & Synthesis.

No further compilation is needed for the alternate persona synthesis step. Running further compilation steps on this type of revision is prohibited by the tools.

Related Information