Intel® FPGA SDK for OpenCL™ Pro Edition: Best Practices Guide

ID

683521

Date

12/19/2022

Public

Product Discontinuance Notification

1. Introduction to Intel® FPGA SDK for OpenCL™ Pro Edition Best Practices Guide

2. Reviewing Your Kernel's report.html File

3. OpenCL Kernel Design Concepts

4. OpenCL Kernel Design Best Practices

5. Profiling Your Kernel to Identify Performance Bottlenecks

6. Strategies for Improving Single Work-Item Kernel Performance

7. Strategies for Improving NDRange Kernel Data Processing Efficiency

8. Strategies for Improving Memory Access Efficiency

9. Strategies for Optimizing FPGA Area Usage

10. Strategies for Optimizing Intel® Stratix® 10 OpenCL Designs

11. Strategies for Improving Performance in Your Host Application

12. Intel® FPGA SDK for OpenCL™ Pro Edition Best Practices Guide Archives

A. Document Revision History for the Intel® FPGA SDK for OpenCL™ Pro Edition Best Practices Guide

2.1. High-Level Design Report Layout

2.2. Reviewing the Summary Report

2.3. Viewing Throughput Bottlenecks in the Design

2.4. Using Views

2.5. Analyzing Throughput

2.6. Reviewing Area Information

2.7. Optimizing an OpenCL Design Example Based on Information in the HTML Report

2.8. Accessing HLD FPGA Reports in JSON Format

4.1. Transferring Data Via Intel® FPGA SDK for OpenCL™ Channels or OpenCL Pipes

4.2. Unrolling Loops

4.3. Optimizing Floating-Point Operations

4.4. Allocating Aligned Memory

4.5. Aligning a Struct with or without Padding

4.6. Maintaining Similar Structures for Vector Type Elements

4.7. Avoiding Pointer Aliasing

4.8. Avoid Expensive Functions

4.9. Avoiding Work-Item ID-Dependent Backward Branching

5.1. Best Practices for Profiling Your Kernel

5.2. Instrumenting the Kernel Pipeline with Performance Counters (-profile)

5.3. Obtaining Profiling Data During Runtime

5.4. Reducing Area Resource Use While Profiling

5.5. Temporal Performance Collection

5.6. Performance Data Types

5.7. Interpreting the Profiling Information

5.8. Profiler Analyses of Example OpenCL Design Scenarios

5.9. Intel® FPGA Dynamic Profiler for OpenCL™ Limitations

8.1. General Guidelines on Optimizing Memory Accesses

8.2. Optimize Global Memory Accesses

8.3. Performing Kernel Computations Using Constant, Local or Private Memory

8.4. Improving Kernel Performance by Banking the Local Memory

8.5. Optimizing Accesses to Local Memory by Controlling the Memory Replication Factor

8.6. Minimizing the Memory Dependencies for Loop Pipelining

8.7. Static Memory Coalescing

6.1.4. Relaxing Loop-Carried Dependency by Inferring Shift Registers

To enable the Intel® FPGA SDK for OpenCL™ Offline Compiler to handle single work-item kernels that carry out double precision floating-point operations efficiently, remove loop-carried dependencies by inferring a shift register.

Consider the following kernel:

1 __kernel void double_add_1 (__global double *arr,

2 int N,

3 __global double *result)

4 {

5 double temp_sum = 0;

6

7 for (int i = 0; i < N; ++i)

8 {

9 temp_sum += arr[i];

10 }

11

12 *result = temp_sum;

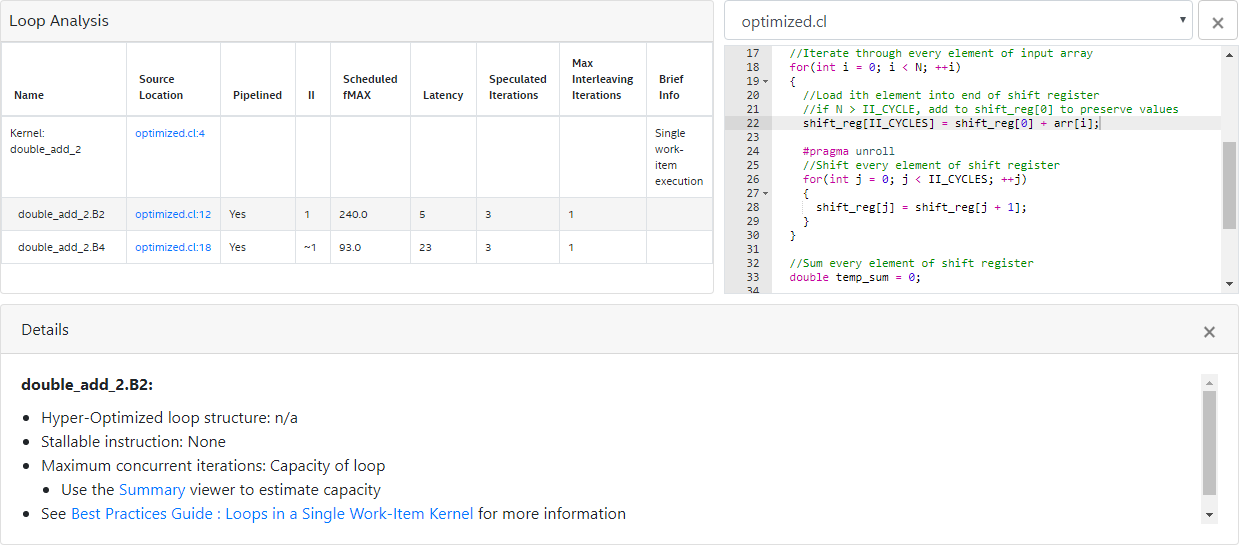

13 }The optimization report for kernel unoptimized resembles the following:

The kernel unoptimized is an accumulator that sums the elements of a double precision floating-point array arr[i]. For each loop iteration, the offline compiler takes 11 cycles to compute the result of the addition and then stores it in the variable temp_sum. Each loop iteration requires the value of temp_sum from the previous loop iteration, which creates a data dependency on temp_sum.

To relax the data dependency, infer the array arr[i] as a shift register.

Below is the restructured kernel optimized:

1 //Shift register size must be statically determinable

2 #define II_CYCLES 12

3

4 __kernel void double_add_2 (__global double *arr,

5 int N,

6 __global double *result)

7 {

8 //Create shift register with II_CYCLE+1 elements

9 double shift_reg[II_CYCLES+1];

10

11 //Initialize all elements of the register to 0

12 for (int i = 0; i < II_CYCLES + 1; i++)

13 {

14 shift_reg[i] = 0;

15 }

16

17 //Iterate through every element of input array

18 for(int i = 0; i < N; ++i)

19 {

20 //Load ith element into end of shift register

21 //if N > II_CYCLE, add to shift_reg[0] to preserve values

22 shift_reg[II_CYCLES] = shift_reg[0] + arr[i];

23

24 #pragma unroll

25 //Shift every element of shift register

26 for(int j = 0; j < II_CYCLES; ++j)

27 {

28 shift_reg[j] = shift_reg[j + 1];

29 }

30 }

31

32 //Sum every element of shift register

33 double temp_sum = 0;

34

35 #pragma unroll

36 for(int i = 0; i < II_CYCLES; ++i)

37 {

38 temp_sum += shift_reg[i];

39 }

40

41 *result = temp_sum;

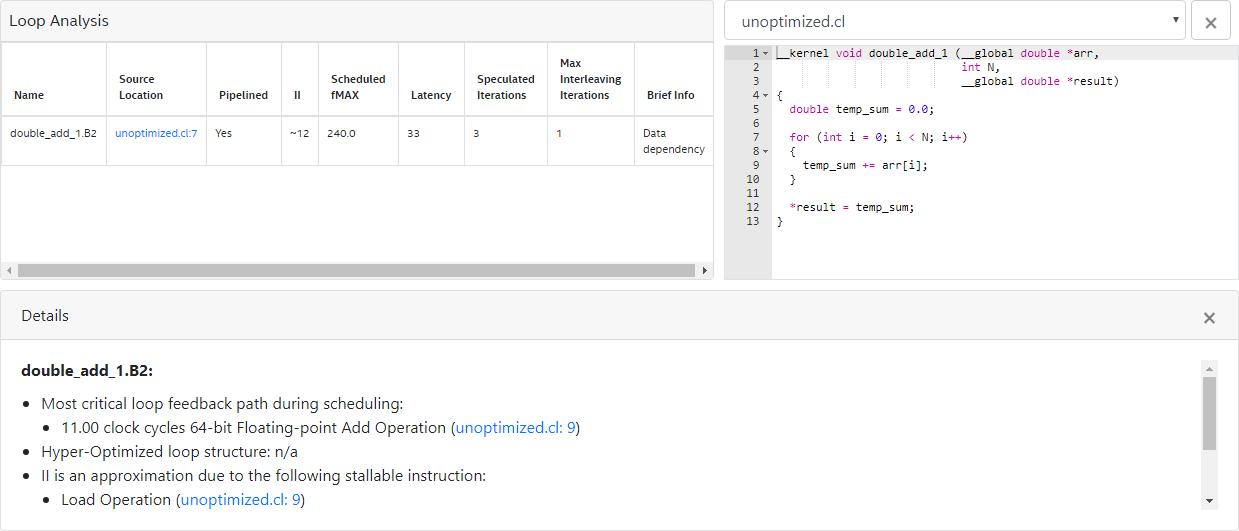

42 }The following optimization report indicates that the inference of the shift register shift_reg[II_CYCLES] successfully removes the data dependency on the variable temp_sum: