AN 866: Mitigating and Debugging Single Event Upsets in Intel® Quartus® Prime Standard Edition

ID

683869

Date

9/28/2021

Public

1.1. Failure Rates

1.2. Mitigating SEU Effects in Embedded User RAM

1.3. Mitigating SEU Effects in Configuration RAM

1.4. Internal Scrubbing

1.5. SEU Recovery

1.6. Intel® Quartus® Prime Software SEU FIT Reports

1.7. Triple-Module Redundancy

1.8. Evaluating a System's Response to Functional Upsets

1.9. CRAM Error Detection Settings Reference

1.10. Document Revision History

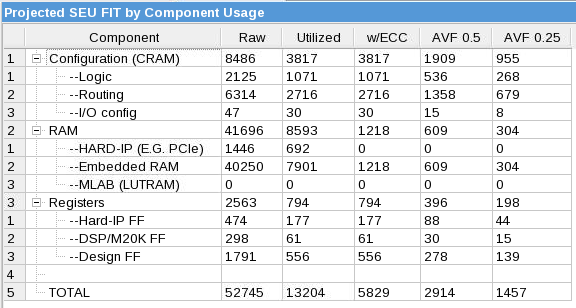

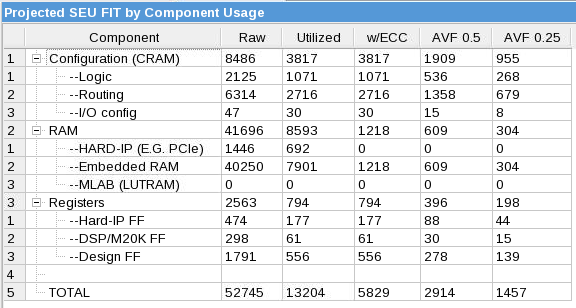

1.6.2. Projected SEU FIT by Component Usage Report

The Projected SEU FIT by Component Usage report shows the different components (or cell types) that comprise the total FIT rate, and SEU FIT calculation results.

An Intel FPGA's sensitivity to soft errors varies by process technology, component type, and your design choices when implementing the component (such as tradeoffs between area/delay and SEU rates). The report shows all bits (the raw FIT), utilized bits (only resources the design actually uses), and the ECC-mitigated bits.

Figure 6. Projected SEU FIT by Component Usage Report