AN 866: Mitigating and Debugging Single Event Upsets in Intel® Quartus® Prime Standard Edition

ID

683869

Date

9/28/2021

Public

1.1. Failure Rates

1.2. Mitigating SEU Effects in Embedded User RAM

1.3. Mitigating SEU Effects in Configuration RAM

1.4. Internal Scrubbing

1.5. SEU Recovery

1.6. Intel® Quartus® Prime Software SEU FIT Reports

1.7. Triple-Module Redundancy

1.8. Evaluating a System's Response to Functional Upsets

1.9. CRAM Error Detection Settings Reference

1.10. Document Revision History

2.3.1.2. About the Advanced SEU Detection IP Core

Use the Advanced SEU Detection (ASD) IP core when SEU tolerance is a design concern.

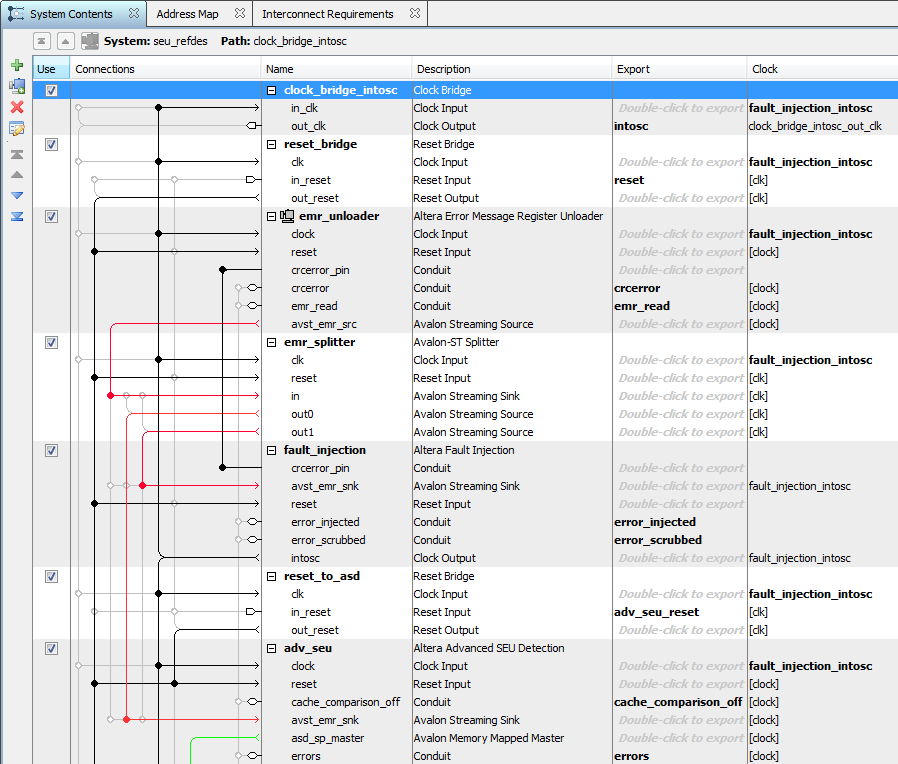

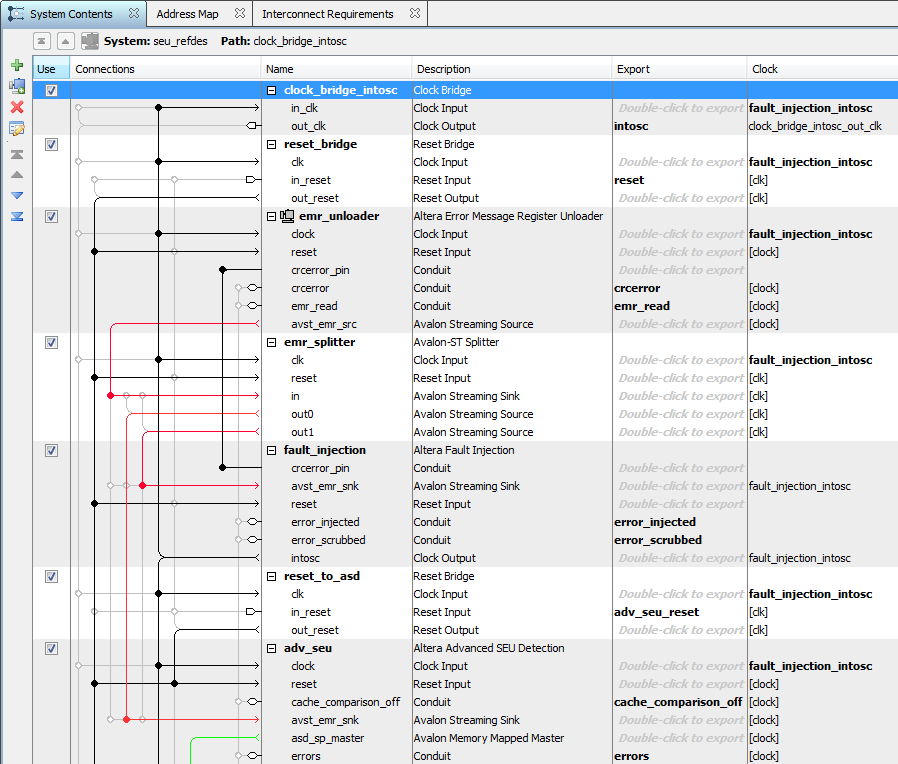

You must use the EMR Unloader IP core with the ASD IP core. Therefore, if you use the ASD IP and the IP in the same design, they must share the EMR Unloader output via an Avalon® -ST splitter component. The following figure shows a Platform Designer system in which an Avalon® -ST splitter distributes the EMR contents to the ASD and IP cores.

Figure 11. Using the ASD and IP in the Same Platform Designer System

Related Information