1. Introduction to Intel® FPGA Design Flow for AMD* Xilinx* Users

2. Technology Comparison

3. FPGA Tools Comparison

4. AMD* Xilinx* to Intel® FPGA Design Conversion

5. Conclusion

6. AN 307: Intel® FPGA Design Flow for AMD* Xilinx* Users Archives

7. Document Revision History for Intel® FPGA Design Flow for AMD* Xilinx* Users

3.3.1. Project Creation

3.3.2. Design Entry

3.3.3. IP Status

3.3.4. Design Constraints

3.3.5. Synthesis

3.3.6. Design Implementation

3.3.7. Finalize Pinout

3.3.8. Viewing and Editing Design Placement

3.3.9. Static Timing Analysis

3.3.10. Generation of Device Programming Files

3.3.11. Power Analysis

3.3.12. Simulation

3.3.13. Hardware Verification

3.3.14. View Netlist

3.3.15. Design Optimization

3.3.16. Techniques to Improve Productivity

3.3.17. Partial Reconfiguration

3.3.18. Cross-Probing in the Quartus® Prime Pro Edition Software

4.2.1.2.1. Memory Mode

4.2.1.2.2. Clocking Mode

4.2.1.2.3. Write and Read Operation Triggering

4.2.1.2.4. Read-During-Write Operation at the Same Address

4.2.1.2.5. Error Correction Code (ECC)

4.2.1.2.6. Byte Enable

4.2.1.2.7. Address Clock Enable

4.2.1.2.8. Parity Bit Support

4.2.1.2.9. Memory Initialization

4.2.1.2.10. Output Synchronous Set/Reset

4.1.1.1. Example of Converting I/O Buffer

In this example, the clk, a, and b inputs are global signals, and the a and b inputs use the IBUFG I/O Standard.

Converting BUFG, IBUFG, and OBUF in Verilog HDL.

Original Verilog HDL Code in the Vivado* Software

module Top (a, b, c, clk);

input a, b, clk;

output c;

reg c_buf;

wire a_buf, b_buf, clk_buf;

BUFG inst1 (.O (clk_buf), .I (clk));

IBUFG #("FALSE", "SSTL12") inst2 (.O (a_buf), .I (a));

IBUFG #("FALSE", "SSTL18_I") inst3 (.O (b_buf), .I (b));

OBUF inst4 (.O (c), .I (c_buf));

always @ (posedge clk_buf) c_buf <= a_buf & b_buf;

endmodule

Converted Verilog HDL Code in the Quartus® Prime Pro Edition Software

module Top (a, b, c, clk);

input a, b, clk;

output c;

reg c_buf;

wire a_buf, b_buf, clk_buf;

assign clk_buf = clk;

assign a_buf = a;

assign b_buf = b;

assign c = c_buf;

always @ (posedge clk_buf)

c_buf <= a_buf & b_buf;

endmodule

Converting BUFG, IBUFG, and OBUF in VHDL.

Original VHDL Code in the Vivado* Software

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY buf_top IS PORT(

a, b : IN STD_ULOGIC; clk : IN STD_ULOGIC; c : OUT STD_ULOGIC);

END buf_top;

ARCHITECTURE Behave OF buf_top IS

SIGNAL a_buf, b_buf, c_buf, clk_buf : STD_ULOGIC; COMPONENT BUFG

PORT (O : OUT STD_ULOGIC; I : IN STD_ULOGIC); END COMPONENT;

COMPONENT IBUFG

generic(IBUF_LOW_PWR : boolean := FALSE;

IOSTANDARD : String := "DEFAULT");

PORT (O : OUT STD_ULOGIC; I : IN STD_ULOGIC); END COMPONENT;

COMPONENT OBUF

PORT (O : OUT STD_ULOGIC; I : IN STD_ULOGIC); END COMPONENT;

BEGIN

inst1 : BUFG

PORT MAP (O => clk_buf, I => clk);

inst2 : IBUFG

generic map(

IBUF_LOW_PWR => FALSE,

IOSTANDARD => "SSTL12")

PORT MAP (O => a_buf,I => a);

inst3 : IBUFG

generic map(

IBUF_LOW_PWR => FALSE,

IOSTANDARD => "SSTL18_I")

PORT MAP (O => b_buf, I => b);

inst4 : OBUF

PORT MAP (O => c, I => c_buf);

PROCESS(clk_buf) BEGIN

IF (clk_buf'event and clk_buf = '1')

THEN c_buf <= a_buf AND b_buf;

END IF;

END PROCESS;

END Behave;

Converted VHDL Code in the Quartus® Prime Pro Edition Software

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY Top IS

PORT(

a, b: IN STD_ULOGIC;

clk: IN STD_ULOGIC;

c: OUT STD_ULOGIC);

END Top;

ARCHITECTURE Behave OF Top IS

SIGNAL a_buf, b_buf, c_buf, clk_buf: STD_ULOGIC;

BEGIN

PROCESS (a, b, c_buf, clk)

BEGIN

clk_buf <= clk;

a_buf <= a;

b_buf <= b;

c <= c_buf;

END PROCESS;

PROCESS(clk_buf)

BEGIN

IF (clk_buf'event and clk_buf = '1') THEN

c_buf <= a_buf AND b_buf;

END IF;

END PROCESS;

END Behave;

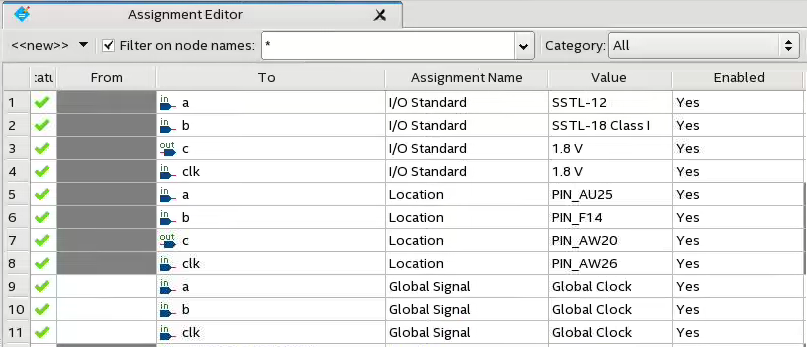

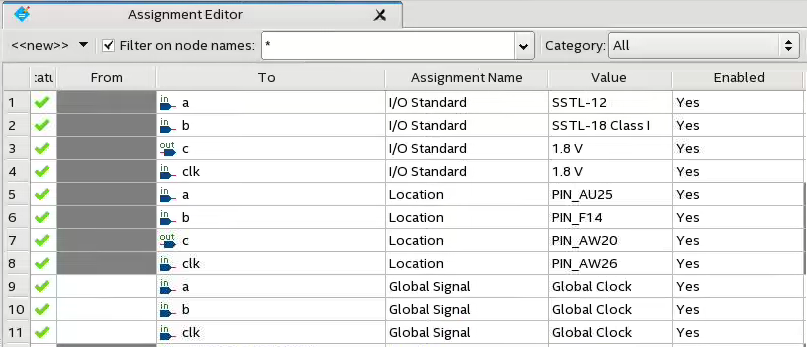

To set the ports with specific assignments in the Quartus® Prime Pro Edition software, use the Assignment Editor.

Figure 11. Global Signal and I/O Standard Assignments Using the Assignment Editor

In the figure, inputs a, b, and clk are assigned as global signals, with clk as the global clock. Input ports a and b are assigned with specific I/O standards, while other ports are automatically assigned with the device-specific default I/O standard.