1. Introduction to Intel® FPGA Design Flow for AMD* Xilinx* Users

2. Technology Comparison

3. FPGA Tools Comparison

4. AMD* Xilinx* to Intel® FPGA Design Conversion

5. Conclusion

6. AN 307: Intel® FPGA Design Flow for AMD* Xilinx* Users Archives

7. Document Revision History for Intel® FPGA Design Flow for AMD* Xilinx* Users

3.3.1. Project Creation

3.3.2. Design Entry

3.3.3. IP Status

3.3.4. Design Constraints

3.3.5. Synthesis

3.3.6. Design Implementation

3.3.7. Finalize Pinout

3.3.8. Viewing and Editing Design Placement

3.3.9. Static Timing Analysis

3.3.10. Generation of Device Programming Files

3.3.11. Power Analysis

3.3.12. Simulation

3.3.13. Hardware Verification

3.3.14. View Netlist

3.3.15. Design Optimization

3.3.16. Techniques to Improve Productivity

3.3.17. Partial Reconfiguration

3.3.18. Cross-Probing in the Quartus® Prime Pro Edition Software

4.2.1.2.1. Memory Mode

4.2.1.2.2. Clocking Mode

4.2.1.2.3. Write and Read Operation Triggering

4.2.1.2.4. Read-During-Write Operation at the Same Address

4.2.1.2.5. Error Correction Code (ECC)

4.2.1.2.6. Byte Enable

4.2.1.2.7. Address Clock Enable

4.2.1.2.8. Parity Bit Support

4.2.1.2.9. Memory Initialization

4.2.1.2.10. Output Synchronous Set/Reset

3.2.1. Command-Line Executable Equivalents

The table and following sections describe and compare the two software flows using command line executables. The examples belong to the fir_filter design, included in the Quartus® Prime Pro Edition installation.

| AMD* Xilinx* Vivado* Software | Quartus® Prime Pro Edition Software | Description | |

|---|---|---|---|

| Non-Project Mode | Project Mode | ||

| read_ip | add_files import_files |

quartus_ipgenerate | IP generation |

| synth_design opt_design |

launch_runs synth_1 | quartus_syn | Elaboration checks for design files and project errors. Translates project design files (for example, RTL or EDA netlist), and maps design elements to device resources. |

| place_design phys_opt_design 7 route_design phys_opt_design 7 |

launch_runs impl_1 | quartus_fit (full compile) OR quartus_fit --plan quartus_fit --place quartus_fit --route quartus_fit --finalize |

Places and routes the device resources into the FPGA. |

| Not Available | quartus_fit --retime 8 | Enabled by default, and runs before finalizing. Moves existing registers into Hyper-Registers for fine-grained performance improvement. | |

| Not Available | quartus_fit --fastforward 8 | Disabled by default. Runs after retime but before finalize. Generates detailed reports that estimate performance gains achievable by making specific RTL modifications. | |

| report_timing | quartus_sta | Performs a static timing analysis on the design. | |

| write_bitstream | quartus_asm | Generates programming file from post-place-and-route design. | |

| report_power | quartus_pow | Performs power estimation on the design. | |

| write_sdf write_verilog write_vhdl |

quartus_eda | Generates output netlist files for use with other EDA tools. | |

| write_checkpoint | quartus_cdb | Saves the snapshot of the design database. | |

| Not Available | quartus_sh --flow compile | Automates the compilation flow. | |

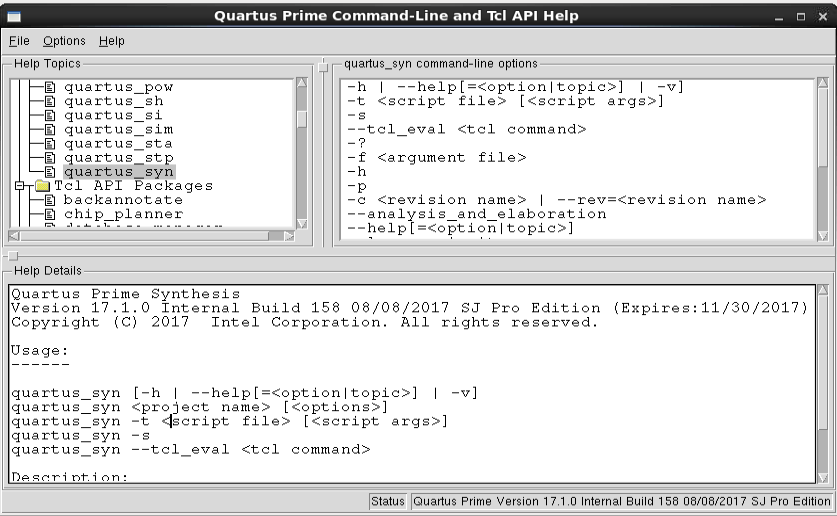

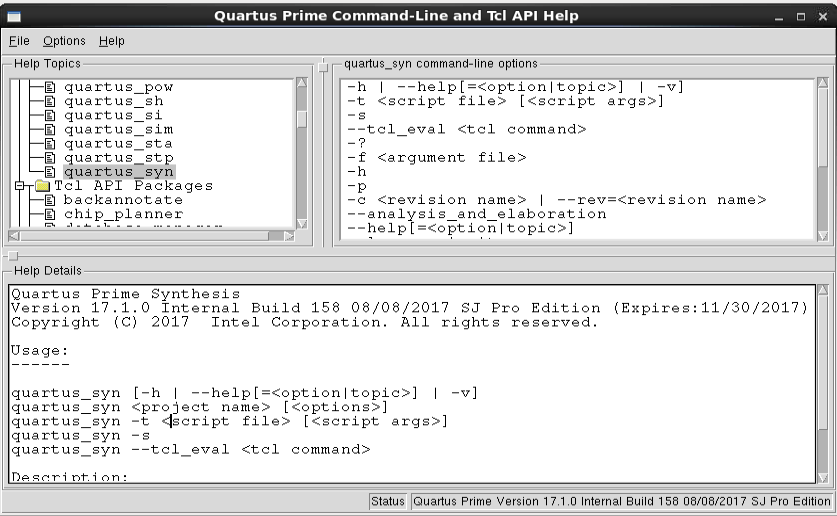

For command line help on any of the Quartus® Prime executables, type <command-line executable> --help at the command prompt. A GUI-enabled help browser is also available that covers all Quartus® Prime command-line executables.

Figure 2. Command-Line HelpStart this browser by typing quartus_sh --qhelp at the command prompt.

Section Content

synth_design

place_design/route_design

report_timing

write_bitstream

write_sdf/write_verilog/write_vhdl

report_power

write_checkpoint

Run Complete Design Flow

7 Optional

8 Retime and Fast-Forward Compilation available only for Agilex™ 7 and Stratix® 10 devices.