Multi Channel DMA for PCI Express* Intel® FPGA IP Design Example User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

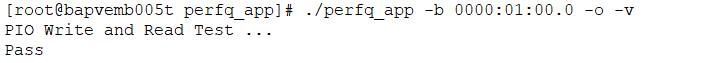

2.4.1.2. Hardware Test Results

- Loopback: 1 MB

- Avalon-MM:

- With validation enabled: ((total available memory) / #channels)

- With validation disabled: 1 MB

- Avalon-ST Packet Generate/Check: 1 MB

- For loopback, Avalon-ST and Avalon-MM design examples (except for the Avalon-ST Packet Generate/Check design example), there is no limit on the transfer size.

- For the Avalon-ST Packet Generate/Check design example, the number of descriptors (transfer size / packet size) should be a modulus of 64 (64 is the default file size).

The -a option specifies the number of threads. For this option, you can provide any number that is a factor of the total number of queues required to distribute the traffic equally among the available cores in the system.

For example, for a system with 64 channels of bidirectional traffic, there is a maximum of 128 possible queues. Hence, the -a option can accept these values: 1,2,4,8,16,32,64,128. If you use -a 128, the 128 queues are distributed among 128 cores. However, if the number of cores in the system is limited, you can use smaller values for a. If you use -a 4, the 128 queues are distributed among 4 cores (with each core handling 32 queues). A higher number of queues per core does lead to a decrease in performance.