1.2.1. Understanding the Different PTP Clocks

1.2.2. Precision Time Protocol (PTP) Synchronization Process

1.2.3. Functional Flow For A 1588 Ordinary Clock Master/Slave Mode System

1.2.4. Functional Flow For A 1588 Transparent Clock Master/Slave Mode System

1.2.5. Functional Flow for A 1588 Boundary Clock Mode System

1.2.6. Timestamp Packet Functional Flow in Linux Driver

1.3.2.3. Replacing RBF File

At times, you may need to modify the reference design according to your system requirements and recompile the reference design. You are required to regenerate the altera_eth_10g_1588_ref_design_msgdma_top.qsys file for compilation. Following are the steps to guide you in regenerating the design files and replacing the RBF file into the system image. You are required to use Quartus II Subscription Edition v14.1 for these procedures.

- Download the alt_eth_1588_rd.qsys.zip file to your computer and unzip the folder.

- Launch Quartus II software. In Quartus II software, click File -> Open Project and browse to av_1588_top.qpf file to open the reference design project.

- Once the the project file is open, click on Tools -> Qsys in the Quartus II software.

- In the Qsys interface, click File -> Open and browse to altera_eth_10g_1588_ref_design_msgdma_top.qsys file to open the reference design Qsys file.

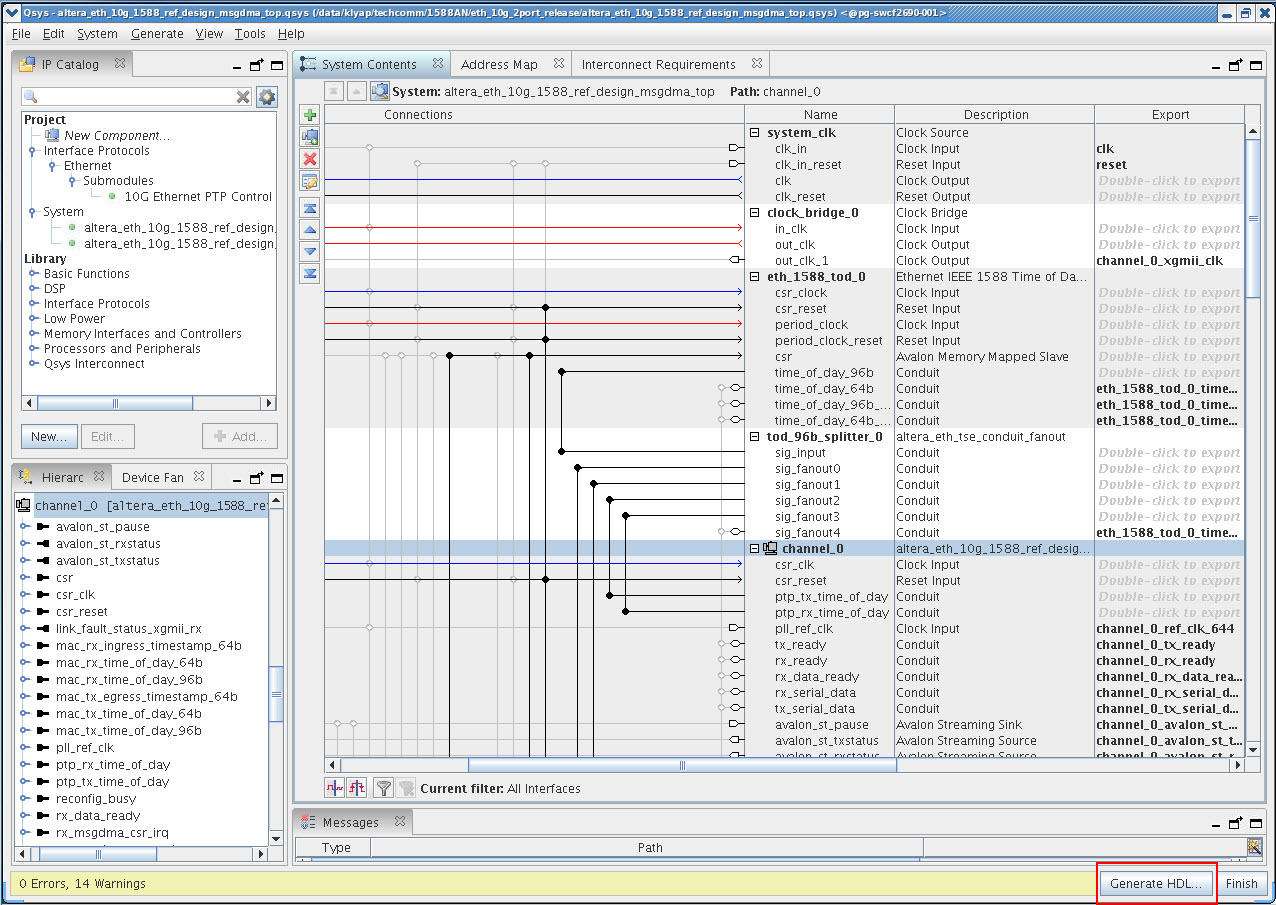

- Once the reference design Qsys file is opened, click Generate HDL.

Figure 19. Generating HDL File in Qsys

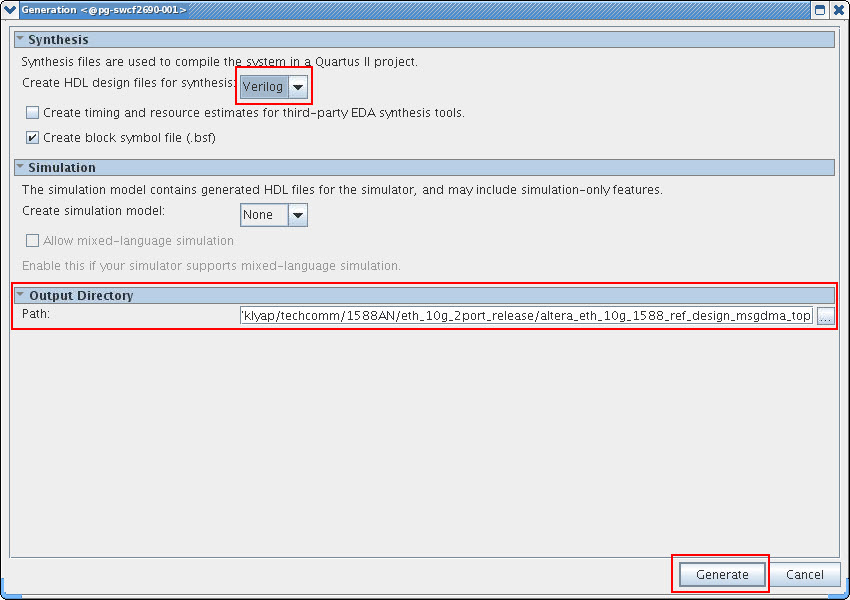

- You will see the Generation dialog box appear. You may choose Verilog or VHDL for synthesis file type.

- Browse to the location where you want to store the generated output files under the Output Directory and click Generate. Click Close once the files generation completed.

Figure 20. Generation Dialog Box

- In Quartus II software, click Processing -> Start Compilation to recompile the reference design. You will see av_1588_top.sof file in the output_files folder once compilation is completed.

- Create a new text file titled option.txt with the following content.

bitstream_compression=on

- At the command prompt in Linux or DOS, type quartus_cpf -o <project_dir>/option.txt -c av_1588_top.sof soc_system.rbf to generate the .rbf (file name tag) file.

- You can replace the soc_system.rbf file in the SD card with the newly generated RBF file.