Video and Vision Processing Suite Intel® FPGA IP User Guide

ID

683329

Date

12/12/2022

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the Video and Vision Processing Suite

2. Getting Started with the Video and Vision Processing IPs

3. Video and Vision Processing IPs Functional Description

4. Video and Vision Processing IP Interfaces

5. Video and Vision Processing IP Registers

6. Video and Vision Processing IPs Software Programming Model

7. Protocol Converter Intel® FPGA IP

8. 3D LUT Intel® FPGA IP

9. AXI-Stream Broadcaster Intel® FPGA IP

10. Chroma Key Intel® FPGA IP

11. Chroma Resampler Intel® FPGA IP

12. Clipper Intel® FPGA IP

13. Clocked Video Input Intel® FPGA IP

14. Clocked Video to Full-Raster Converter Intel® FPGA IP

15. Clocked Video Output Intel® FPGA IP

16. Color Space Converter Intel® FPGA IP

17. Deinterlacer Intel® FPGA IP

18. FIR Filter Intel® FPGA IP

19. Frame Cleaner Intel® FPGA IP

20. Full-Raster to Clocked Video Converter Intel® FPGA IP

21. Full-Raster to Streaming Converter Intel® FPGA IP

22. Genlock Controller Intel® FPGA IP

23. Generic Crosspoint Intel® FPGA IP

24. Genlock Signal Router Intel® FPGA IP

25. Guard Bands Intel® FPGA IP

26. Interlacer Intel® FPGA IP

27. Mixer Intel® FPGA IP

28. Pixels in Parallel Converter Intel® FPGA IP

29. Scaler Intel® FPGA IP

30. Stream Cleaner Intel® FPGA IP

31. Switch Intel® FPGA IP

32. Tone Mapping Operator Intel® FPGA IP

33. Test Pattern Generator Intel® FPGA IP

34. Video Frame Buffer Intel® FPGA IP

35. Video Streaming FIFO Intel® FPGA IP

36. Video Timing Generator Intel® FPGA IP

37. Warp Intel® FPGA IP

38. Design Security

39. Document Revision History for Video and Vision Processing Suite User Guide

22.4.1. Achieving Genlock Controller Free Running (for Initialization or from Lock to Reference Clock N)

22.4.2. Locking to Reference Clock N (from Genlock Controller IP free running)

22.4.3. Setting the VCXO hold over

22.4.4. Restarting the Genlock Controller IP

22.4.5. Locking to Reference Clock N New (from Locking to Reference Clock N Old)

22.4.6. Changing to Reference Clock or VCXO Base Frequencies (switch between p50 and p59.94 video formats and vice-versa)

22.4.7. Disturbing a Reference Clock (a cable pull)

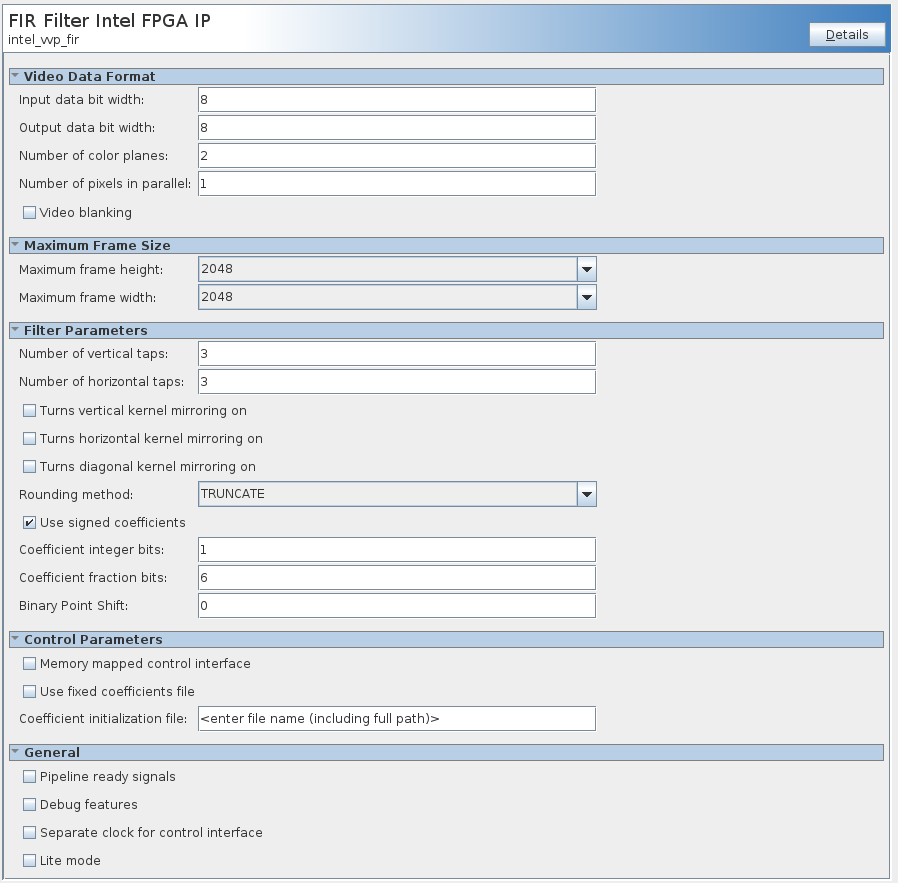

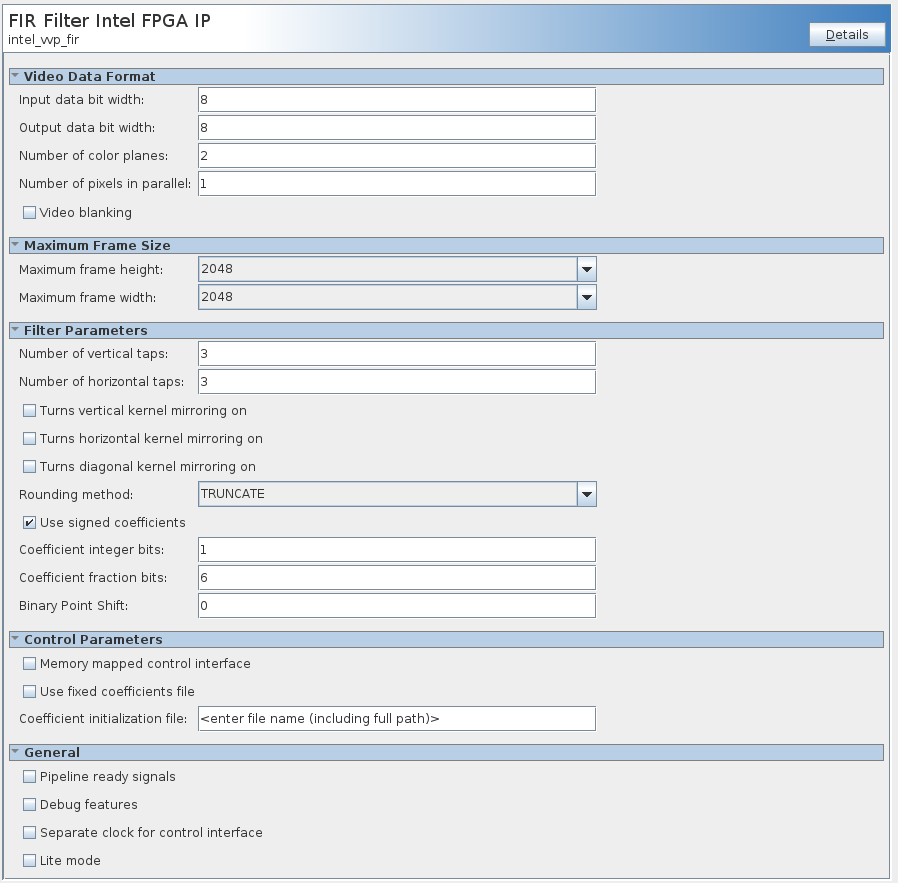

18.2. FIR Filter Parameters

The IP offers run- and compile-time parameters.

| Parameter | Values | Description |

|---|---|---|

| Video Data Format | ||

| Input bits per color sample | 8 to 16 | Select the number of input bits per color sample. |

| Output bits per color sample | 8 to 16 | Select the number of output bits per color sample. |

| Number of color planes | 1 to 4 | Select the number of color planes per pixel. |

| Number of pixels in parallel | 1 to 8 | Select the number of pixels in parallel. |

| Video Blanking | On or off | Turn on when the filtered video has blanking |

| Maximum Frame Size | ||

| Maximum field height | 2048-16384 | Specify the maximum height of incoming frames |

| Maximum field width | 2048-16384 | Specify the maximum width of incoming frames |

| Filter Parameters | ||

| Vertical filter taps | 3-16 | Height of the FIR filter |

| Horizontal filter taps | 3-16 | Width of the FIR filter |

| Vertical kernel mirroring | On or Off | Turn on enable vertical symmetry |

| Horizontal kernel mirroring | On or Off | Turn on enable horizontal symmetry |

| Diagonal kernel mirroring | On or Off | Turn on diagonal symmetry |

| Rounding method | Truncate, round half up or round half even | Select the rounding method of choice for the output of the filter |

| Signed coefficients | On or Off | Turn on signed coefficients |

| Coefficient integer bits | 0-18 | Select the number of the coefficient’s integer bits. The sum of integer bits + fraction bits cannot exceed 18 |

| Coefficient fraction bits | 0-18 | Select the number of the coefficient’s fraction bits. The sum of integer bits + fraction bits cannot exceed 18 |

| Control Parameters | ||

| Runtime control | On or off | Turn on run-time coefficient loading via the Avalon memory-mapped interface |

| Use fixed coefficients file | On or off | Turn on for a fixed coefficient file that the IP loads at compile time |

| Fixed coefficients file | <file path> | Specify the fixed coefficients file path |

Figure 42. FIR Filter Parameters