Quartus® Prime Pro Edition User Guide: Design Compilation

A newer version of this document is available. Customers should click here to go to the newest version.

1.7.4. Post-Synthesis Static Timing Analysis (STA)

The Synopsys* Design Constraint (SDC) on RTL supports the underlying technology to read the constraints early in the compilation flow and use them in the later stages of the Quartus® Prime compilation. However, you can run the flow even without RTL SDCs where you can view the synthesized timing netlist.

Post-synthesis STA defaults to a simple average value delay model based on the types of blocks a net connects. "Average Value" interconnect (IC) delay model to control STA after synthesis. Using the STA_POST_SYN_DELAY_MODEL QSF, you can switch to the "Zero Value" IC delay model to exclude interconnect delays from the timing model.

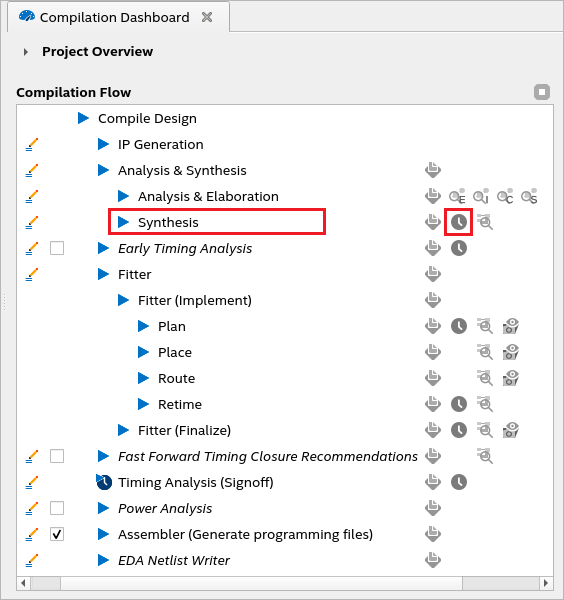

You can now access the Timing Analyzer right after design synthesis in the compilation dashboard, as shown in the following image:

Post-synthesis static timing analysis (STA) uses a timing netlist representing core blocks and their contents. It also includes periphery blocks (but nothing inside them is modeled) and cell delays of the core blocks. Routing delays between core blocks is represented by IC delays that use the average interconnect model mentioned above.

Post-synthesis STA timing netlist provides you with an early view of your design's core timing. You can run timing analysis reports and constraint diagnostic commands, allowing you to examine SDC-on-RTL constraints.

Perform the following steps to run post-synthesis STA:

- Create an Quartus® Prime software project using your design RTL and associated SDC-on-RTL SDC file.

- Run Analysis and Elaboration compilation stage on your design as follows:

quartus_syn --analysis_and_elaboration <design>

- Perform Synthesis on your design as follows:

quartus_syn -–synthesis <design>

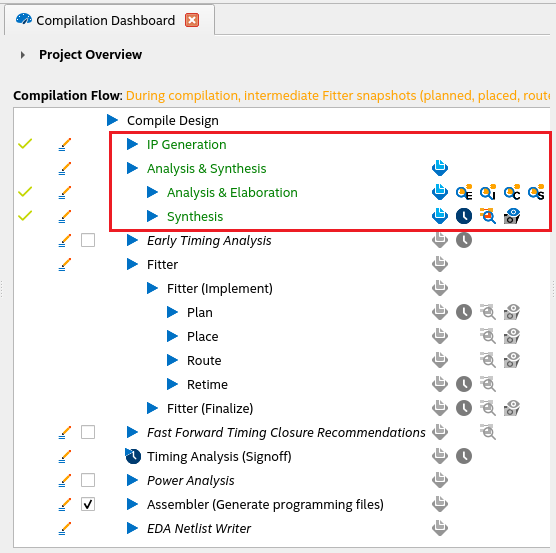

You can also perform the above steps using the Quartus® Prime software GUI, as shown in the following image:

After running post-synthesis STA on your design, you can use the Timing Analyzer conventionally. However, a fundamental difference in the netlist topography is that the post-synthesis STA timing netlist has no connectivity inside any periphery block.

For post-synthesis constraints, Intel recommends using an SDC-on-RTL file. In cases where this is not possible, post-synthesis STA introduces the SDC_FILE -read_during_post_syn_and_not_post_fit_timing_analysis QSF argument, which is used to inform the Timing Analyzer to include a conventional SDC in the list of SDCs to be read during a post-synthesis STA session. This QSF is beneficial for blocks that do not have SDC-on-RTL constraints available. Since the post-synthesis STA netlist differs from the post-plan STA netlist, conventional SDCs written for the post-plan netlist might not function during post-synthesis STA. By creating a new category of SDC files, you can identify scripts you want to load during post-synthesis STA.