Quartus® Prime Pro Edition User Guide: Design Compilation

ID

683236

Date

4/01/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1.1. Compilation Overview

1.2. Using the Compilation Dashboard

1.3. Design Netlist Infrastructure

1.4. Using the Node Finder

1.5. Precompiled Component (PCC) Generation Flow

1.6. Analysis & Elaboration Flow

1.7. Design Synthesis

1.8. Design Place and Route

1.9. Incremental Optimization Flow

1.10. Fast Forward Compilation Flow

1.11. Full Compilation Flow

1.12. Compilation Monitoring Mode

1.13. Exporting Compilation Results

1.14. Integrating Other EDA Tools

1.15. Compiler Optimization Techniques

1.16. Synthesis Language Support

1.17. Synthesis Settings Reference

1.18. Fitter Settings Reference

1.19. Design Compilation Revision History

1.7.3.1. Registering the SDC-on-RTL SDC File

1.7.3.2. Applying the SDC-on-RTL Constraints

1.7.3.3. Inspecting SDC-on-RTL Constraints

1.7.3.4. Creating Constraints in SDC-on-RTL SDC Files

1.7.3.5. Using Entity-Based SDC-on-RTL Constraints

1.7.3.6. Types of SDC Files Used in the Quartus® Prime Software

1.7.3.7. Example: Using SDC-on-RTL Features

1.13.1. Exporting a Version-Compatible Compilation Database

1.13.2. Importing a Version-Compatible Compilation Database

1.13.3. Creating a Design Partition

1.13.4. Exporting a Design Partition

1.13.5. Reusing a Design Partition

1.13.6. Viewing Quartus Database File Information

1.13.7. Clearing Compilation Results

2.1. Factors Affecting Compilation Results

2.2. Strategies to Reduce the Overall Compilation Time

2.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

2.4. Reducing Placement Time

2.5. Reducing Routing Time

2.6. Reducing Static Timing Analysis Time

2.7. Setting Process Priority

2.8. Reducing Compilation Time Revision History

1.5. Precompiled Component (PCC) Generation Flow

Precompiled Components (PCC) generation flow is a compilation stage that runs between IP Generation and Analysis & Synthesis stages on the compilation dashboard. It synthesizes and caches the results of the Intel® FPGA IP components in your design.

PCC generation reduces Synthesis compile time through the following steps and allows you to iterate and go to post-synthesis timing analysis stages faster and reduce the development cycle time:

- Synthesizes Intel® FPGA IP components in your design.

- Generates and caches IP compilation results in your project's ocs_cache_dir (IP cache) directory.

- Reuses the IP cache in subsequent Synthesis runs.

Figure 6. PCC Generation

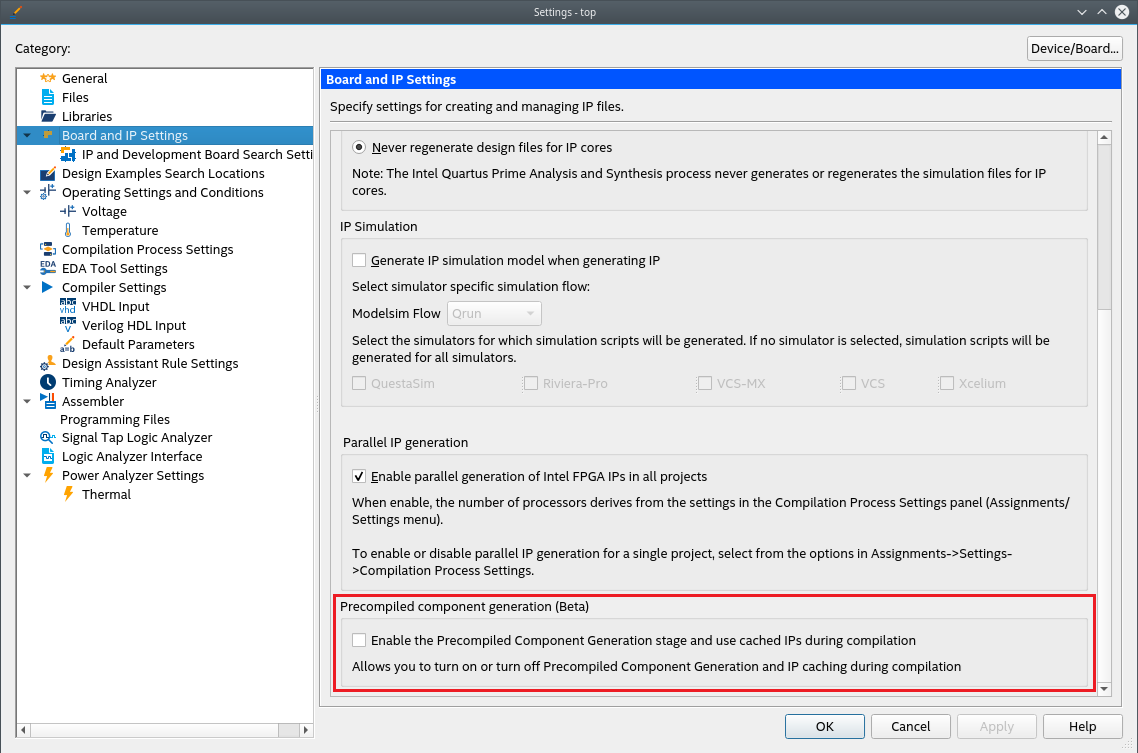

By default, the PCC generation flow is disabled. You can enable it from Assignments > Settings > Board and IP Settings dialog as shown in the following:

If the PCC generation flow compiles successfully, you can view the Precompiled Components compilation report for each IP that participates in the flow under the Compilation Reports dialog.

Advantages of PCC Generation Flow

- Each unique IP is generated only once and cached, so the subsequent Synthesis run does not perform PCC generation if you have not modified any IP in your design.

- If you modify any IP, the PCC generation flow synthesizes only that IP and skips synthesizing the remaining IPs.

- The PCC generation process occurs in parallel for each IP.

- Synthesis compile time savings scales with the proportion of the design that is IP.