AN 584: Timing Closure Methodology for Advanced FPGA Designs

1.6.4. Metastability Issues

Clock-domain-crossing (CDC) signals can cause metastability on the capturing clock domain register. To reduce the possibility of going metastable, you must synchronize all signals between asynchronous clock domains with multiple stages of synchronizing registers.

Signals with a source in one clock domain may be registered in another clock domain, causing the data input to fail the setup or hold time requirements of the destination register. This may cause the output of the latching register to go to an intermediate state between a logical 1 and a logical 0. Although this intermediate value eventually resolves to a ‘1’ or ‘0,’ the issue is the indeterminate time the value takes to resolve itself.

Generally, a minimum of two stages is recommended. The Intel® Quartus® Prime software by default is set to look for three register stages to place as close together to obtain better Mean Time Between Failures (MTBF).

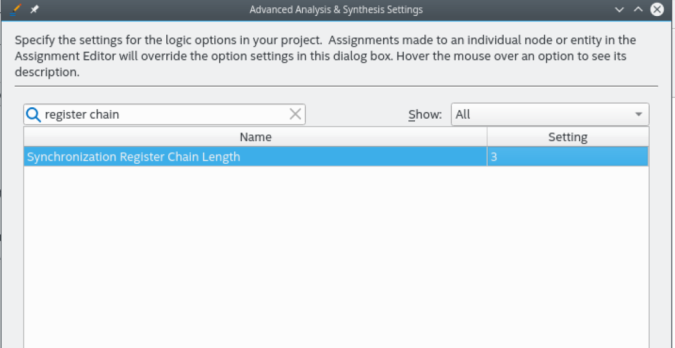

To change this default value, click Assignments > Settings > Compiler Settings > Optimization Mode > Advanced Settings (Synthesis) and specify a value for Synchronization Register Chain Length.

The Intel® Quartus® Prime software can analyze designs for metastability, and offers recommendations to reduce metastability. You can compute MTBF on circuit parameters. You should increase the MTBF as much as possible.

Isolating failures caused by metastability can be problematic because they can appear as sporadic device failures, which are hard to debug. Increasing the MTBF might reduce the occurrence of such failures.

Metastability problems in your design can appear as incorrectly operating state machines. Symptoms include skipped states, or state machines that do not recover from a stage or lock-up. State machines might also miss triggering events that cause state transitions. Such problems might occur when you do not synchronize control signals to a state machine coming from other clock domains.

By synchronizing all asynchronous control signals, you can ensure that these signals remain stable for an integral number of clock cycles, and trigger transitions appropriately.

For more information about metastability, refer to the Managing Metastability in Intel® Quartus® Prime Pro Edition User Guide: Design Recommendations.