A newer version of this document is available. Customers should click here to go to the newest version.

1. Introduction

2. Avalon® -ST Single-Clock and Dual-Clock FIFO Cores

3. Avalon® -ST Serial Peripheral Interface Core

4. SPI Core

5. SPI Agent/JTAG to Avalon® Host Bridge Cores

6. Intel eSPI Agent Core

7. eSPI to LPC Bridge Core

8. Ethernet MDIO Core

9. Intel FPGA 16550 Compatible UART Core

10. UART Core

11. JTAG UART Core

12. Intel FPGA Avalon® Mailbox Core

13. Intel FPGA Avalon® Mutex Core

14. Intel FPGA Avalon® I2C (Host) Core

15. Intel FPGA I2C Agent to Avalon® -MM Host Bridge Core

16. Intel FPGA Avalon® Compact Flash Core

17. EPCS/EPCQA Serial Flash Controller Core

18. Intel FPGA Serial Flash Controller Core

19. Intel FPGA Serial Flash Controller II Core

20. Intel FPGA Generic QUAD SPI Controller Core

21. Intel FPGA Generic QUAD SPI Controller II Core

22. Interval Timer Core

23. Intel FPGA Avalon FIFO Memory Core

24. On-Chip Memory (RAM and ROM) Intel FPGA IP

25. On-Chip Memory II (RAM or ROM) Intel FPGA IP

26. Optrex 16207 LCD Controller Core

27. PIO Core

28. PLL Cores

29. DMA Controller Core

30. Modular Scatter-Gather DMA Core

31. Scatter-Gather DMA Controller Core

32. SDRAM Controller Core

33. Tri-State SDRAM Core

34. Video Sync Generator and Pixel Converter Cores

35. Intel FPGA Interrupt Latency Counter Core

36. Performance Counter Unit Core

37. Vectored Interrupt Controller Core

38. Avalon® -ST Data Pattern Generator and Checker Cores

39. Avalon® -ST Test Pattern Generator and Checker Cores

40. System ID Peripheral Core

41. Avalon® Packets to Transactions Converter Core

42. Avalon® -ST Multiplexer and Demultiplexer Cores

43. Avalon® -ST Bytes to Packets and Packets to Bytes Converter IP

44. Avalon® -ST Delay Core

45. Avalon® -ST Round Robin Scheduler Core

46. Avalon® -ST Splitter Core

47. Avalon® -MM DDR Memory Half Rate Bridge Core

48. Intel FPGA GMII to RGMII Converter Core

49. HPS GMII to RGMII Adapter Intel® FPGA IP

50. Intel FPGA MII to RMII Converter Core

51. HPS GMII to TSE 1000BASE-X/SGMII PCS Bridge Core Intel® FPGA IP

52. Intel FPGA HPS EMAC to Multi-rate PHY GMII Adapter Core

53. Intel FPGA MSI to GIC Generator Core

54. Cache Coherency Translator Intel® FPGA IP

55. Altera ACE5-Lite Cache Coherency Translator

56. Lightweight UART Core

9.2.1. Unsupported Features

9.2.2. Interface

9.2.3. General Architecture

9.2.4. 16550 UART General Programming Flow Chart

9.2.5. Configuration Parameters

9.2.6. DMA Support

9.2.7. FPGA Resource Usage

9.2.8. Timing and Fmax

9.2.9. Avalon® -MM Agent

9.2.10. Over-run/Under-run Conditions

9.2.11. Hardware Auto Flow-Control

9.2.12. Clock and Baud Rate Selection

14.5.2.1. Transfer Command FIFO (TFR_CMD)

14.5.2.2. Receive Data FIFO (RX_DATA)

14.5.2.3. Control Register (CTRL)

14.5.2.4. Interrupt Status Enable Register (ISER)

14.5.2.5. Interrupt Status Register (ISR)

14.5.2.6. Status Register (STATUS)

14.5.2.7. TFR CMD FIFO Level (TFR CMD FIFO LVL)

14.5.2.8. RX Data FIFO Level (RX Data FIFO LVL)

14.5.2.9. SCL Low Count (SCL LOW)

14.5.2.10. SCL High Count (SCL HIGH)

14.5.2.11. SDA Hold Count (SDA HOLD)

23.6.1. altera_avalon_fifo_init()

23.6.2. altera_avalon_fifo_read_status()

23.6.3. altera_avalon_fifo_read_ienable()

23.6.4. altera_avalon_fifo_read_almostfull()

23.6.5. altera_avalon_fifo_read_almostempty()

23.6.6. altera_avalon_fifo_read_event()

23.6.7. altera_avalon_fifo_read_level()

23.6.8. altera_avalon_fifo_clear_event()

23.6.9. altera_avalon_fifo_write_ienable()

23.6.10. altera_avalon_fifo_write_almostfull()

23.6.11. altera_avalon_fifo_write_almostempty()

23.6.12. altera_avalon_write_fifo()

23.6.13. altera_avalon_write_other_info()

23.6.14. altera_avalon_fifo_read_fifo()

23.6.15. altera_avalon_fifo_read_other_info()

24.1. Core Overview

24.2. Component-Level Design for On-Chip Memory

24.3. Platform Designer System-Level Design for On-Chip Memory

24.4. Simulation for On-Chip Memory

24.5. Quartus® Prime Project-Level Design for On-Chip Memory

24.6. Board-Level Design for On-Chip Memory

24.7. Example Design with On-Chip Memory

24.8. On-Chip Memory (RAM and ROM) Intel FPGA IP Revision History

25.1. Core Overview

25.2. Embedded Memory Architecture and Features

25.3. Component-Level Configurations

25.4. Interface Signals

25.5. Control and Status Registers

25.6. Software Programming Model

25.7. Platform Designer System-Level Design for On-Chip Memory II

25.8. Simulation for On-Chip Memory II

25.9. Quartus® Prime Project-Level Design for On-Chip Memory II

25.10. Board-Level Design for On-Chip Memory II

25.11. Example Design with On-Chip Memory II

25.12. On-Chip Memory II (RAM and ROM) Intel FPGA IP Revision History

30.1. Core Overview

30.2. Feature Description

30.3. mSGDMA Interfaces and Parameters

30.4. mSGDMA Descriptors

30.5. Register Map of mSGDMA

30.6. Programming Model

30.7. Modular Scatter-Gather DMA Prefetcher Core

30.8. Driver Implementation

30.9. Example Code Using mSGDMA Core

30.10. Modular Scatter-Gather DMA Core Revision History

30.5.1. Status Register

30.5.2. Control Register

30.5.3. Write Fill Level Register

30.5.4. Read Fill Level Register

30.5.5. Response Fill Level Register

30.5.6. Write Sequence Number Register

30.5.7. Read Sequence Number Register

30.5.8. Component Configuration 1 Register

30.5.9. Component Configuration 2 Register

30.5.10. Component Type Register

30.5.11. Component Version Register

30.8.1. alt_msgdma_standard_descriptor_async_transfer

30.8.2. alt_msgdma_extended_descriptor_async_transfer

30.8.3. alt_msgdma_descriptor_async_transfer

30.8.4. alt_msgdma_standard_descriptor_sync_transfer

30.8.5. alt_msgdma_extended_descriptor_sync_transfer

30.8.6. alt_msgdma_descriptor_sync_transfer

30.8.7. alt_msgdma_construct_standard_st_to_mm_descriptor

30.8.8. alt_msgdma_construct_standard_mm_to_st_descriptor

30.8.9. alt_msgdma_construct_standard_mm_to_mm_descriptor

30.8.10. alt_msgdma_construct_standard_descriptor

30.8.11. alt_msgdma_construct_extended_st_to_mm_descriptor

30.8.12. alt_msgdma_construct_extended_mm_to_st_descriptor

30.8.13. alt_msgdma_construct_extended_mm_to_mm_descriptor

30.8.14. alt_msgdma_construct_extended_descriptor

30.8.15. alt_msgdma_register_callback

30.8.16. alt_msgdma_open

30.8.17. alt_msgdma_write_standard_descriptor

30.8.18. alt_msgdma_write_extended_descriptor

30.8.19. alt_msgdma_init

30.8.20. alt_msgdma_irq

31.7.1. Data Structure

31.7.2. SG-DMA API

31.7.3. alt_avalon_sgdma_do_async_transfer()

31.7.4. alt_avalon_sgdma_do_sync_transfer()

31.7.5. alt_avalon_sgdma_construct_mem_to_mem_desc()

31.7.6. alt_avalon_sgdma_construct_stream_to_mem_desc()

31.7.7. alt_avalon_sgdma_construct_mem_to_stream_desc()

31.7.8. alt_avalon_sgdma_enable_desc_poll()

31.7.9. alt_avalon_sgdma_disable_desc_poll()

31.7.10. alt_avalon_sgdma_check_descriptor_status()

31.7.11. alt_avalon_sgdma_register_callback()

31.7.12. alt_avalon_sgdma_start()

31.7.13. alt_avalon_sgdma_stop()

31.7.14. alt_avalon_sgdma_open()

37.5.6.1. altera_vic_driver.enable_preemption

37.5.6.2. altera_vic_driver.enable_preemption_into_new_register_set

37.5.6.3. altera_vic_driver.enable_preemption_rs_<n>

37.5.6.4. altera_vic_driver.linker_section

37.5.6.5. altera_vic_driver.<name>.vec_size

37.5.6.6. altera_vic_driver.<name>.irq<n>_rrs

37.5.6.7. altera_vic_driver.<name>.irq<n>_ril

37.5.6.8. altera_vic_driver.<name>.irq<n>_rnmi

37.5.6.9. Default Settings for RRS and RIL

37.5.6.10. VIC BSP Design Rules for Intel FPGA HAL Implementation

37.5.6.11. RTOS Considerations

39.1. Core Overview

39.2. Resource Utilization and Performance

39.3. Test Pattern Generator

39.4. Test Pattern Checker

39.5. Hardware Simulation Considerations

39.6. Software Programming Model

39.7. Test Pattern Generator API

39.8. Test Pattern Checker API

39.9. Avalon® -ST Test Pattern Generator and Checker Cores Revision History

39.7.1. data_source_reset()

39.7.2. data_source_init()

39.7.3. data_source_get_id()

39.7.4. data_source_get_supports_packets()

39.7.5. data_source_get_num_channels()

39.7.6. data_source_get_symbols_per_cycle()

39.7.7. data_source_set_enable()

39.7.8. data_source_get_enable()

39.7.9. data_source_set_throttle()

39.7.10. data_source_get_throttle()

39.7.11. data_source_is_busy()

39.7.12. data_source_fill_level()

39.7.13. data_source_send_data()

39.8.1. data_sink_reset()

39.8.2. data_sink_init()

39.8.3. data_sink_get_id()

39.8.4. data_sink_get_supports_packets()

39.8.5. data_sink_get_num_channels()

39.8.6. data_sink_get_symbols_per_cycle()

39.8.7. data_sink_set enable()

39.8.8. data_sink_get_enable()

39.8.9. data_sink_set_throttle()

39.8.10. data_sink_get_throttle()

39.8.11. data_sink_get_packet_count()

39.8.12. data_sink_get_symbol_count()

39.8.13. data_sink_get_error_count()

39.8.14. data_sink_get_exception()

39.8.15. data_sink_exception_is_exception()

39.8.16. data_sink_exception_has_data_error()

39.8.17. data_sink_exception_has_missing_sop()

39.8.18. data_sink_exception_has_missing_eop()

39.8.19. data_sink_exception_signalled_error()

39.8.20. data_sink_exception_channel()

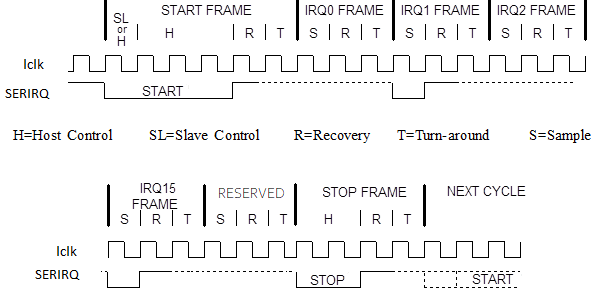

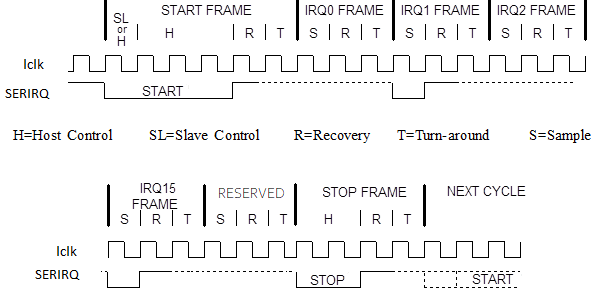

7.4.4. SERIRQ Interrupt Event

The LPC bridge supports 16 lines IRQ/Data serializer by sampling the event of SERIRQ signal from the LPC interface. A SERIRQ cycle transfer consists of three frame types:

- Start Frame: The agent device drives the SERIRQ line low to indicate the start of IRQ transmission.

- IRQ/Data Frames (several): Peripherals transmit the IRQ information. The eSPI bridge host supports 16 IRQ data frames. During the sample phase, the SERIRQ device must drive the SERIRQ low, if and only if, its detected IRQ/Data value is low. And if its detected IRQ/Data value is high, SERIRQ must be left tri-stated. During the recovery phase, the device must drive the SERIRQ high, if and only if, it had driven the SERIRQ low during the sample phase.

- Stop Frame: The Host Controller initiates a Stop frame to terminate SERIRQ activity after all IRQ/Data Frames have completed. A Stop Frame is indicated when the SERIRQ is low for two clock cycles. Stop frame occurs at 53-54 clock cycles past the Start frame.

Figure 27. SERIRQ Event Timing Diagram

The start frame is 4 clock cycles, stop frame is 2 clock cycles, and the IRQ/Data frames clock cycles are stated below:

| IRQ/Data Frame | Sampled Signal | Number of Clocks after Start Frame |

|---|---|---|

| 1 | IRQ0 | 2 |

| 2 | IRQ1 | 5 |

| 3 | SMI# | 8 |

| 4 | IRQ3 | 11 |

| 5 | IRQ4 | 14 |

| 6 | IRQ5 | 17 |

| 7 | IRQ6 | 20 |

| 8 | IRQ7 | 23 |

| 9 | IRQ8 | 26 |

| 10 | IRQ9 | 29 |

| 11 | IRQ10 | 32 |

| 12 | IRQ11 | 35 |

| 13 | IRQ12 | 38 |

| 14 | IRQ13 | 41 |

| 15 | IRQ14 | 44 |

| 16 | IRQ15 | 47 |

| 17 | Reserved | - |

Once the LPC bridge samples and derives the SERIRQ event, it translates the IRQ/Data Frame into VW index bit as below:

IRQ VW information can be sent to the eSPI host only through GET_VWIRE command during transition period.

| SERIRQ Sampled Signal | VW Index Group | VW Data Bit |

|---|---|---|

| SMI# | 6h | Bit 2 |

| IRQ0 to IRQ15 | 00h | Bit 0 - Bit 15 |

| Interrupt Source Type | Interrupt Source Level | Agent to Host IRQ Virtual Wire (Active High) |

|---|---|---|

| Active low | 0 → 1 | De-assertion. IRQ VW (Level=’0’) sent. |

| Active low | 1 → 0 | Assertion. IRQ VW (Level=’1’) sent. |