Arria V GZ Avalon-MM Interface for PCIe Solutions: User Guide

A.4.9. Minimizing BAR Sizes and the PCIe Address Space

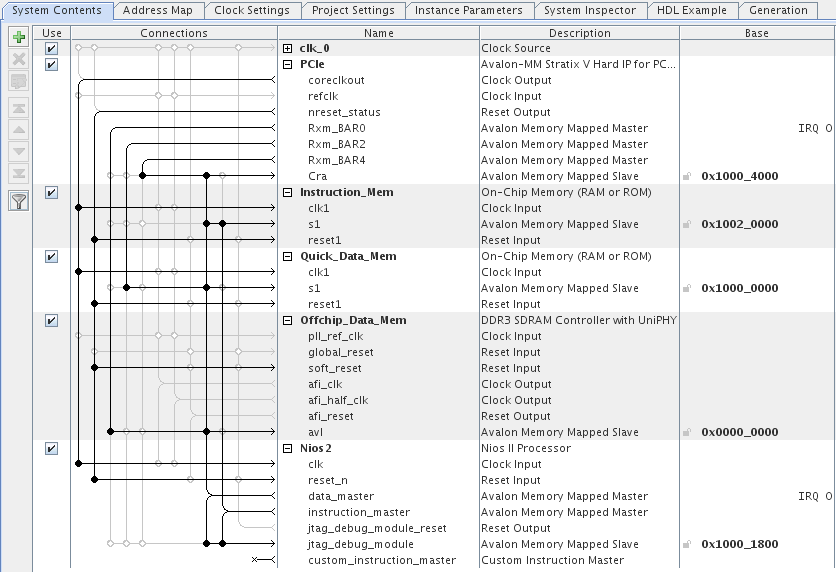

For designs that include multiple BARs, you may need to modify the base address assignments auto‑assigned by Platform Designer in order to minimize the address space that the BARs consume. For example, consider a Platform Designer system with the following components:

- Offchip_Data_Mem DDR3 (SDRAM Controller with UniPHY) controlling 256 MB of memory—Platform Designer auto‑assigned a base address of 0x00000000

- Quick_Data_Mem (On-Chip Memory (RAM or ROM)) of 4 KB—Platform Designer auto‑assigned a base address of 0x10000000

- Instruction_Mem (On-Chip Memory (RAM or ROM)) of 64 KB—Platform Designer auto‑assigned a base address of 0x10020000

- PCIe (Avalon‑MM Arria® V GZ Hard IP for PCI Express)

- Cra (Avalon‑MM Slave)—auto assigned base address of 0x10004000

- Rxm_BAR0 connects to Offchip_Data_Mem DD R3 avl

- Rxm_BAR2 connects to Quick_Data_Mem s1

- Rxm_BAR4 connects to PCIe. Cra Avalon MM Slave

- Nios2 (Nios® II Processor)

- data_master connects to PCIe Cra, Offchip_Data_Mem DDR3 avl, Quick_Data_Mem s1, Instruction_Mem s1, Nios2 jtag_debug_module

- instruction_master connects to Instruction_Mem s1

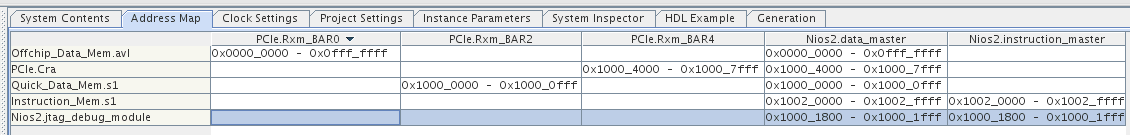

The auto‑assigned base addresses result in the following three large BARs:

- BAR0 is 28 bits. This is the optimal size because it addresses the Offchip_Data_Mem which requires 28 address bits.

- BAR2 is 29 bits. BAR2 addresses the Quick_Data_Mem which is 4 KB. It should only require 12 address bits; however, it is consuming 512 MBytes of address space.

- BAR4 is also 29 bits. BAR4 address PCIe Cra is 16 KB. It should only require 14 address bits; however, it is also consuming 512 MB of address space.

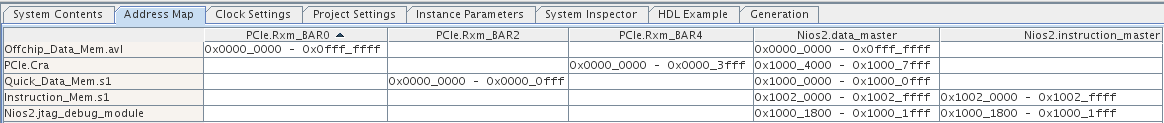

This design is consuming 1.25 GB of PCIe address space when only 276 MB are actually required. The solution is to edit the address map to place the base address of each BAR at 0x0000_0000. The following figure illustrates the optimized address map.

For cases where the BAR Avalon-MM RX master port connects to more than one Avalon‑MM slave, assign the base addresses of the slaves sequentially and place the slaves in the smallest power‑of‑two‑sized address space possible. Doing so minimizes the system address space used by the BAR.