1. Getting Started

2. Development Kit Overview

3. Power Up the Development Kit

4. Board Test System (BTS)

5. Development Kit Hardware and Configuration

6. Document Revision History for Intel® Stratix® 10 DX FPGA Development Kit User Guide

A. Development Kit Components

B. Safety and Regulatory Information

C. Compliance and Conformity Information

A.1. Components Overview

A.2. Power, Thermal, and Mechanical Considerations

A.3. Clock Circuits

A.4. Memory Interface

A.5. PCIe Interface

A.6. UPI Interface

A.7. Transceiver Signals: PCIe and UPI Interface

A.8. SlimSAS Connector

A.9. QSFP Network Interface

A.10. I2C Interface

A.11. QSPI Flash Memory

A.9. QSFP Network Interface

The Intel® Stratix® 10 DX FPGA Development Kit supports two QSFP28 connectors each connecting to the E-Tile (9A) transceivers. Each port can operate at 2x50G or 4x25G. These two ports support ZQSFP56 SR Optical modules as well as 3M DAC electrical cables.

The FPC202 dual port controller (from Texas Instruments) serves as the low speed signal aggregator that makes up the Dual 100Gpbs Ethernet interfaces. The FPC202 aggregates all low speed and I2C signals across two ports and presents it as a single management interface to the host. The current limiters TP2557 (from Texas Instruments) also limit the current, in case if there is a short in the DAC electrical cables or Optical modules.

Figure 47. Transceiver QSFP-56 Two Ports of 25GbE

The E-tile (9A) of the Intel® Stratix® 10 DX FPGA provides eight transceiver channels, channel 0-3 are routed to QSFP0 and channel 12-15 are routed to QSFP1. The transceiver bank requires 156.25 MHz clocks for 28 Gbps NRZ and 325.50 MHz clocks for 56 Gbps PAM4. These clocks must have RPM jitter< 250 fs.

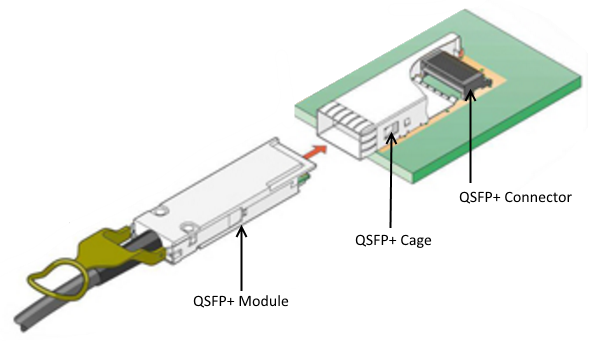

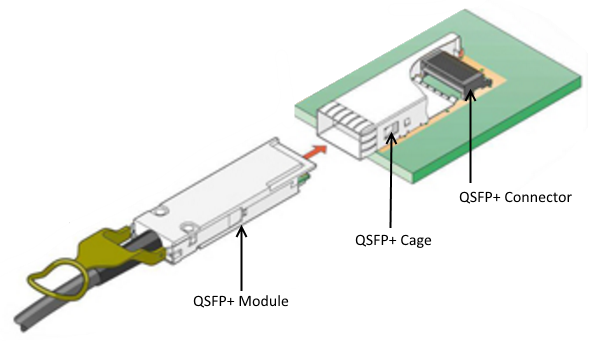

Figure 48. QSFP Connector