Arria V GZ Avalon-ST Interface for PCIe Solutions: User Guide

ID

683297

Date

12/21/2020

Public

1. Datasheet

2. Getting Started with the Arria® V GZ Hard IP for PCI Express

3. Getting Started with the Configuration Space Bypass Mode Qsys Example Design

4. Parameter Settings

5. Interfaces and Signal Descriptions

6. Registers

7. Interrupts

8. Error Handling

9. PCI Express Protocol Stack

10. Transaction Layer Protocol (TLP) Details

11. Throughput Optimization

12. Design Implementation

13. Additional Features

14. Hard IP Reconfiguration

15. Transceiver PHY IP Reconfiguration

16. Testbench and Design Example

17. Debugging

A. Lane Initialization and Reversal

B. Document Revision History

1.1. Arria® V GZ Avalon-ST Interface for PCIe Datasheet

1.2. Release Information

1.3. Device Family Support

1.4. Configurations

1.5. Avalon-ST Example Designs

1.6. Debug Features

1.7. IP Core Verification

1.8. Resource Utilization

1.9. Recommended Speed Grades

1.10. Creating a Design for PCI Express

2.1.1. Generating the Testbench

2.1.2. Simulating the Example Design

2.1.3. Generating Synthesis Files

2.1.4. Understanding the Files Generated

2.1.5. Understanding Simulation Log File Generation

2.1.6. Understanding Physical Placement of the PCIe IP Core

2.1.7. Compiling the Design in the Qsys Design Flow

2.1.8. Modifying the Example Design

2.1.9. Using the IP Catalog To Generate Your Arria® V GZ Hard IP for PCI Express as a Separate Component

3.3.1. Timing for Configuration Read to Function 0 for the 256-Bit Avalon-ST Interface

3.3.2. Timing for Configuration Write to Function 0 for the 256-Bit Avalon-ST Interface

3.3.3. Timing for Memory Write and Read of Function 1 256-Bit Avalon-ST Interface

3.3.4. Partial Transcript for Configuration Space Bypass Simulation

5.1. Clock Signals

5.2. Reset, Status, and Link Training Signals

5.3. ECRC Forwarding

5.4. Error Signals

5.5. Interrupts for Endpoints

5.6. Interrupts for Root Ports

5.7. Completion Side Band Signals

5.8. Configuration Space Bypass Mode Interface Signals

5.9. Parity Signals

5.10. LMI Signals

5.11. Transaction Layer Configuration Space Signals

5.12. Hard IP Reconfiguration Interface

5.13. Power Management Signals

5.14. Physical Layer Interface Signals

6.1. Correspondence between Configuration Space Registers and the PCIe Specification

6.2. Type 0 Configuration Space Registers

6.3. Type 1 Configuration Space Registers

6.4. PCI Express Capability Structures

6.5. Intel-Defined VSEC Registers

6.6. CvP Registers

6.7. Uncorrectable Internal Error Mask Register

6.8. Uncorrectable Internal Error Status Register

6.9. Correctable Internal Error Mask Register

6.10. Correctable Internal Error Status Register

16.6.1. ebfm_barwr Procedure

16.6.2. ebfm_barwr_imm Procedure

16.6.3. ebfm_barrd_wait Procedure

16.6.4. ebfm_barrd_nowt Procedure

16.6.5. ebfm_cfgwr_imm_wait Procedure

16.6.6. ebfm_cfgwr_imm_nowt Procedure

16.6.7. ebfm_cfgrd_wait Procedure

16.6.8. ebfm_cfgrd_nowt Procedure

16.6.9. BFM Configuration Procedures

16.6.10. BFM Shared Memory Access Procedures

16.6.11. BFM Log and Message Procedures

16.6.12. Verilog HDL Formatting Functions

16.7.1. Changing Between Serial and PIPE Simulation

16.7.2. Using the PIPE Interface for Gen1 and Gen2 Variants

16.7.3. Viewing the Important PIPE Interface Signals

16.7.4. Disabling the Scrambler for Gen1 and Gen2 Simulations

16.7.5. Disabling 8B/10B Encoding and Decoding for Gen1 and Gen2 Simulations

16.7.6. Changing between the Hard and Soft Reset Controller

3.3. Simulating the Example Design

Follow these steps to simulate the Qsys system using ModelSim:

- In a terminal window, change to the <working_dir>/top/testbench/mentor directory.

- Start the ModelSim simulator by typing vsim.

- To compile the simulation, type the following commands in the terminal window:

- source msim_setup.tcl (The msim_setup.tcl file defines aliases.

- ld_debug (The ld_debug command argument stops optimizations, improving visibility in the ModelSim waveforms. )

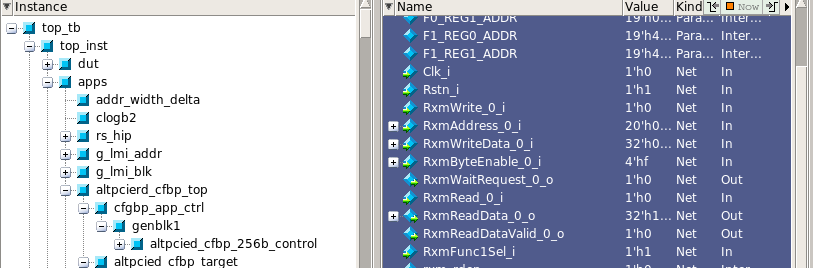

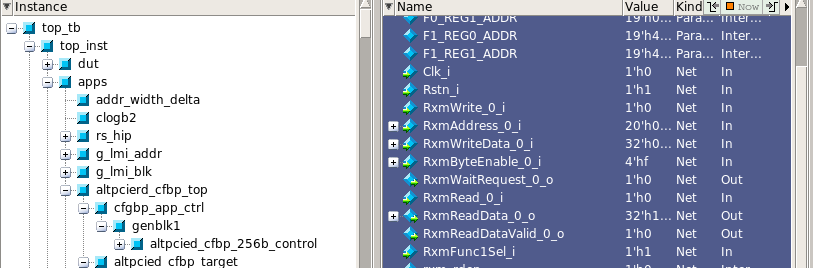

The following figure shows the design hierarchy for the Configuration Space Bypass Example Design after compilation.

Figure 11. Design Hierarchy for the Configuration Space Bypass Example Design for 256-Bit Avalon-ST Interface

- To observe the simulation, on the ModelSim View menu, select wave. Then add some key interfaces to the wave window. The following four interfaces under the /top_tb/top_inst/apps/altpcierd_cfbp_top/cfgbp_app_ctrl/genblk1 illustrate the TX and RX interfaces, the current state, and configuration.

- *RxSt*

- *TxSt*

- *Rxm*

- *_state*

- cfg_*

- To run the simulation, type the following command: run -all

Note: By default, the simulation is serial, to simulate using the parallel PIPE interface, you can change the default value of the serial_sim_hwtcl parameter from 1 to 0 in altera_pcie_cfgbp_ed/top/testbench/top_tb/simulation/top_tb.v. After changing that value, you must recompile the simulation to pick up the new value of the serial_sim_hwtcl parameter before running the simulation.

Section Content

Timing for Configuration Read to Function 0 for the 256-Bit Avalon-ST Interface

Timing for Configuration Write to Function 0 for the 256-Bit Avalon-ST Interface

Timing for Memory Write and Read of Function 1 256-Bit Avalon-ST Interface

Partial Transcript for Configuration Space Bypass Simulation