GTS SDI II IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs

ID

823543

Date

5/30/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

2.4.2. Test Description

The SDI II design example simulation only checks for the assertion of trs_locked signal and the number of transceiver reconfiguration triggered after every video standard switching.

Figure 26. Video Standard Sequence - Triple Rate DesignThe following figure shows the sequence of the video standard for triple-rate design:

Figure 27. Video Standard Sequence - Multirate Design

The following figure shows the sequence of the video standard for multi-rate design:

For single-rate design, the IP tests one video standard:

- HD single-rate – HD

- 3G single-rate – 3G Level A 10-bit Multiplex

- 12G single rate – 12G 10-bit Multiplex Type 1

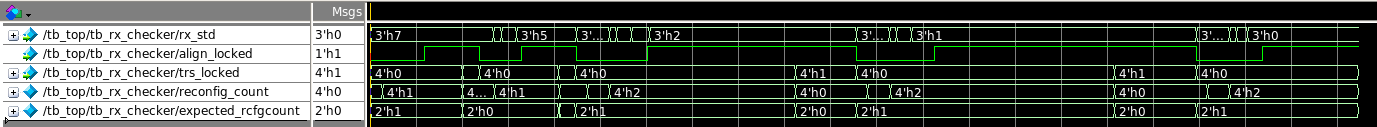

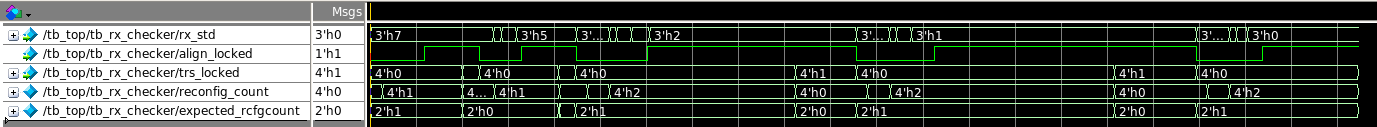

Figure 28. Simulation Waveform

| Testbench signal | Description |

|---|---|

| /tb_top/tb_rx_checker/rx_std | Video standard keeps switching after obtaining lock signal |

| /tb_top/tb_rx_checker/align_locked | Lock signals from IP |

| /tb_top/tb_rx_checker/trs_locked | |

| /tb_top/tb_rx_checker/reconfig_count | Actual number of transceiver reconfiguration triggered after every video standard switching versus the expected number of configurations. |

| /tb_top/tb_rx_checker/expected_rcfgcount |

The following message in the simulator indicates a succesful test: