AN 744: Scalable Triple Speed Ethernet Reference Design for Arria 10 Devices

ID

683785

Date

5/13/2016

Public

1.7.3. Test Case: Design With the IEEE 1588v2 Feature

The simulation performs the following steps.

- Starts up the design with an operating speed of 1 Gbps.

- Configures the MAC, PHY speed, and FIFO buffer for the channels.

- Waits until the design asserts the channel_ready signal for each channel.

- Sends the following packets:

- Basic data frame with PTP over Ethernet, PTP Sync Message, and 1-step PTP.

- VLAN data frame with PTPover UDP/IPv4, PTP Sync Message, and 1-step PTP.

- Stacked VLAN data frame with PTP over UDP/IPv6, PTP Sync Message, and 2-step PTP.

- Basic data frame with PTP over Ethernet, PTP Delay Request Message, and 1-step PTP.

- VLAN data frame with PTPover UDP/IPv4, PTP Delay Request Message, and 2-step PTP.

- SVLAN data frame with PTP over UDP/IPv6, PTP Delay Request Message, and 1-step PTP.

- Repeats steps 2 to 4 for operating speeds 100 Mbps and 10 Mbps.

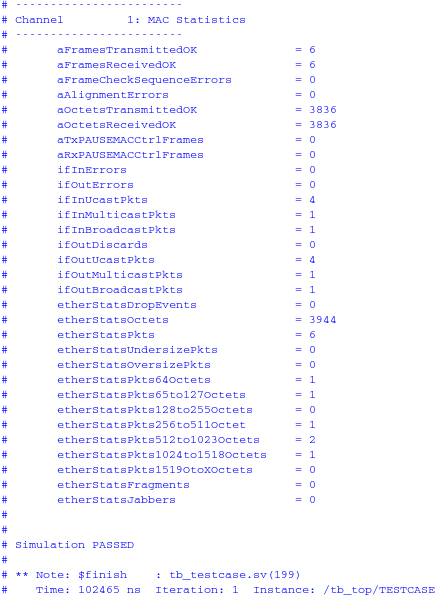

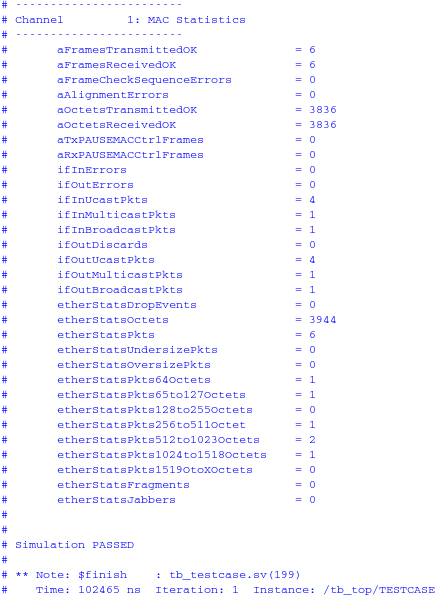

When simulation ends, the values of the MAC statistics counters are displayed in the transcript window. The transcript window also displays PASSED if the RX Avalon-ST interface of channel 0 received all packets successfully.

Figure 5. Simulation Results