Intel® Quartus® Prime Pro Edition User Guide: Design Compilation

A newer version of this document is available. Customers should click here to go to the newest version.

2.3.2.2. Post-Synthesis Static Timing Analysis (STA)

Post-synthesis static timing analysis (STA) uses a timing netlist comprising core block delays with no routing or periphery delays. This provides you with an early view of your design's core timing. You can run timing analysis reports and some design rules.

Perform the following steps to run post-synthesis STA:

- Create an Intel® Quartus® Prime software project using your design RTL and associated SDC-on-RTL SDC file.

- In the DNI flow, run Analysis and Elaboration compilation stage on your design as follows:

quartus_syn --dni --analysis_and_elaboration <design> - Perform Synthesis on your design as follows:

quartus_syn --dni -–synthesis <design> - Perform post-synthesis STA on your design as follows:

quartus_sta --post_syn <design>

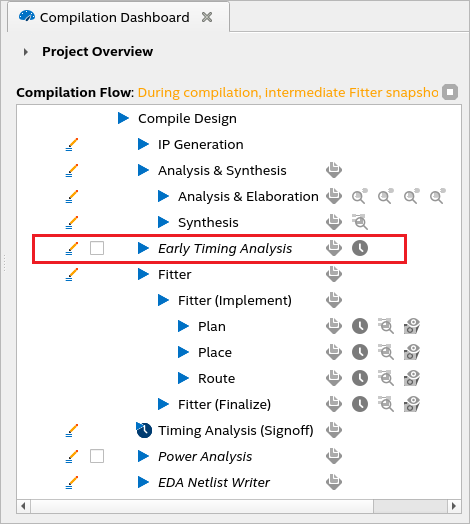

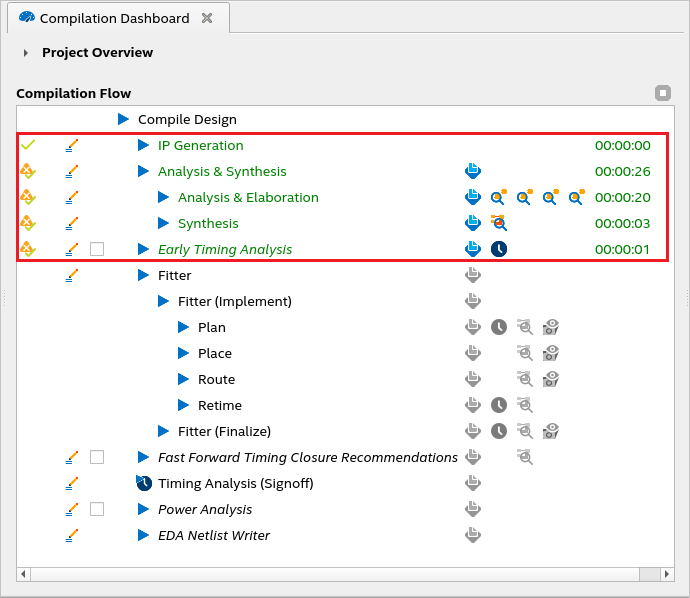

You can also perform the above steps using the Intel® Quartus® Prime software GUI with DNI flow enabled, as shown in the following image:

After running post-synthesis STA on your design, you can use the Timing Analyzer conventionally. However, a fundamental difference in the netlist topography is that the post-synthesis STA timing netlist has no connectivity inside any periphery block.

For conventional SDC scripts, post-synthesis STA introduces the SYN_SDC_FILE QSF variable, which you can use to add an SDC file to the QSF during post-synthesis STA. This QSF is beneficial for blocks that do not have SDC-on-RTL constraints available. Since the post-synthesis STA netlist differs from the post-plan STA netlist, conventional SDCs written for the post-plan netlist might not function during post-synthesis STA. By creating a new category of SDC files, you can identify scripts you want to load during post-synthesis STA.