Intel Agilex® 7 F-Series and I-Series FPGA Memory Subsystem IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

6.3.2. BCAM Insert Operations

To perform an insert operation, follow these steps in the AXI-Lite interface:

- Write the key to the key_n registers.

- Write the result to the result_n registers.

- Write to the mgmt_ctrl register, specifying op_type = 0x1.

- Poll the mgmt_ctrl register until the busy bit = 0x0.

If you attempt to insert an entry that already exists, or to fill the table beyond the nominal MAX_ENTRIES capacity, the operation will fail. Insert operations are otherwise expected succeed for all realistic data sets, though it is technically possible for an operation to fail because the management logic times out while waiting for the cuckoo swapping key to become unoccupied (the timeout in cycles is accessed by the Gen_Ctrl register insert_timeout field or specified by MAX_INSERT_ITERATIONS parameter).

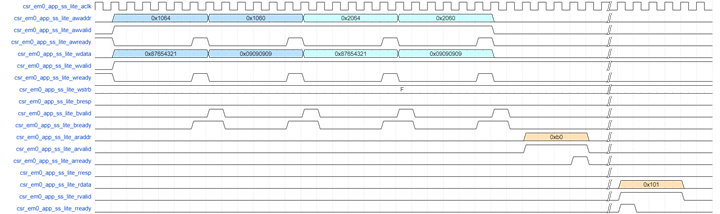

The following image shows an insert operation on BCAM of key = 0x8765432109090909, where:

- The address of mgmt_ctrl register is 0xb0, due to CSR_BASEADDR + CSR_ADDROFF + offset -> 0 + 0x60 + 0x50 = 0xB0.

- The address of key_n register is 0x1060, due to CSR_BASEADDR + CSR_ADDROFF + offset -> 0 + 0x60 + 0x1000 = 0x1060.

- The address of result_n register is 0x2060, due to CSR_BASEADDR + CSR_ADDROFF + offset -> 0 + 0x60 + 0x2000 = 0x2060.