A newer version of this document is available. Customers should click here to go to the newest version.

2.4.1. Reset Request Interface

Nios® V processor includes an optional reset request facility. The reset request facility consists of reset_req and reset_req_ack signals.

- Launch the Nios® V Processor IP Parameter Editor.

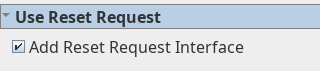

- On the Use Reset Request setting, turn on the Add Reset Request Interface option.

Figure 10. Enable Nios® V Processor Reset Request

The reset_req signal acts like an interrupt. When you assert the reset_req, you are requesting reset to the core. The core waits for any outstanding bus transaction to complete its operation. For example, if there is a pending memory access transaction, core waits for a complete response. Similarly, core accepts any pending instruction response but does not issue instruction request after receiving the reset_req signal.

- Complete all pending operation

- Flush internal pipeline

- Set the instruction Program Counter to reset vector

- Reset core

The whole reset operation takes a few clock cycles. The reset_req must remain asserted until reset_req_ack is asserted indicating core reset operation has successfully completed. Failure to do so results in core’s state being non-deterministic.