Quartus® Prime Pro Edition User Guide: Design Optimization

A newer version of this document is available. Customers should click here to go to the newest version.

6.1. Location Assignment Optimization Guidelines

Guideline: Assigning Logic to Specific Locations

As part of design optimization, you may want to assign logic in your design to specific locations in the target device floorplan. You may want to make this type of assignment to preserve a good placement result, or to replicate a result in future compiles. In most cases, design partitions are the best way to preserve placement. For more information, refer to Creating a Design Partition in Quartus Prime Pro Edition User Guide: Design Compilation

Guideline: Assigning the Location of One or Two Registers

Sometimes, you may want to assign the location of one or two registers or combinational nodes. In cases where the amount of logic is extremely small, a design partition is not usually practical. If you want to restrict placement to an area of the floorplan, you can use a Logic Lock region placement constraint. For more information, refer to Defining Logic Lock Placement Constraints.

Guideline: Assigning a Register to a Specific Location in an ALM

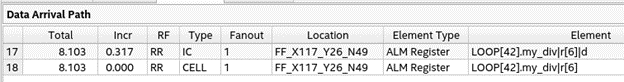

If you want to assign a register to a specific location in an ALM, you must know the specific location you want to assign. The specific location includes the X and Y coordinates of the LAB that contains the ALM, as well as the sub-location of the register in the ALM in the LAB. The easiest way to find this information during design optimization is to start from a compiled version of the design, and review a timing path report in the Timing Analyzer. Use the string in the Location column as the value for a location assignment.

For example, to assign the LOOP[42].my_div|r[6] register to the location shown in Example Compilation Results, use the following QSF statement:

set_location_assignment -to LOOP[42].my_div|r[6] FF_X117_Y26_N49

Guideline: Making Assignments to Compiler-Modified Nodes

If you make location assignments to registers that the Compiler modifies or optimizes during compilation, is unlikely that the Compiler will honor the assignment in subsequent compiles. Compiler-modified or optimized registers include a suffix that begins with a tilde character (~). If the Compiler modifies a register during compilation, the suffix is likely to change on subsequent compiles as you change other parts of the circuit. When the suffix changes, the name associated with the assignment also changes, so the Compiler does not honor the assignment.

Guideline: Assigning Combinational Logic to Specific Locations

Generally it is not worth assigning combinational logic to specific locations. Combinational logic names are more likely to change in subtle ways from one compile to another. When the names change, any location assignments are ignored if the names don’t match.