4.2.3. Controller Parameters for High Bandwidth Memory (HBM2) Interface Intel® FPGA IP

| Display Name | Description |

|---|---|

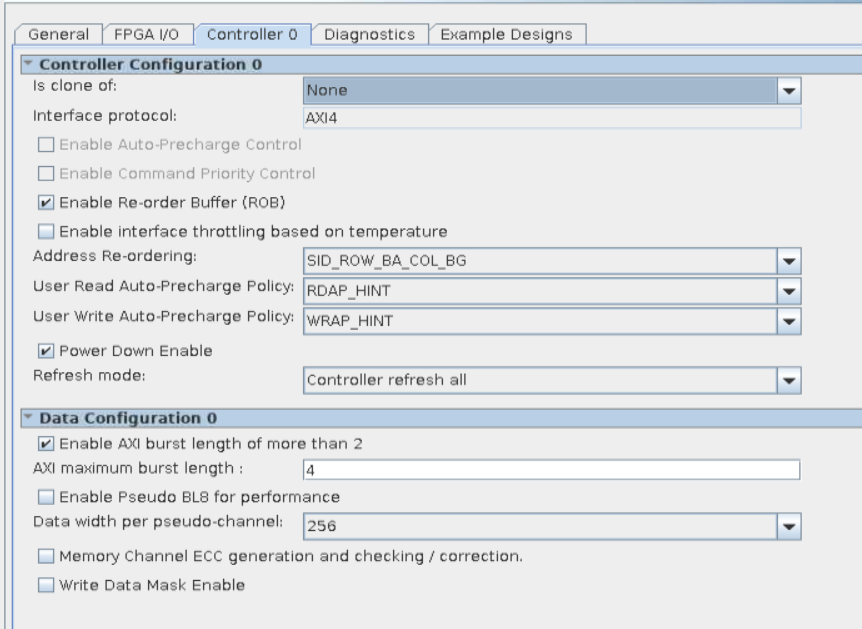

| Is clone of | Set this option to make this controller a clone of the selected controller. Parameters are copied from the specified controller. This parameter applies when you select more than one HBM2 controller. Set this parameter if you want one controller to have the same settings as another. |

| Interface Protocol | AXI or AVMM ( Avalon® memory-mapped) is displayed, based on the interface protocol that you select for the channel on the General tab. |

| Enable Auto Precharge Control | Select this parameter to enable the auto-precharge control on the controller top level. If you assert the auto-precharge control signal while requesting a read or write burst, you can specify whether the controller should close (auto-precharge) the currently open page at the end of the read or write burst, potentially making a future access to a different page of the same bank faster. Applicable to Avalon® -MM channel only. |

| Enable Command Priority Control | Select this parameter to enable user-requested command priority control on the controller top level. This parameter instructs the controller to treat a read or write request as high-priority. The controller attempts to fill high priority requests sooner, to reduce latency. Connect this interface to the conduit of your logic block that determines when the external memory interface IP treats the read or write request as a high priority command. Applicable to Avalon-MM channel only. |

| Enable Re-order buffer | Specifies that read data be reordered to match the order in which transactions are issued. If you disable this feature, the Read Data provided at the AXI Interface is not expected to follow the same order in which the Read Requests were issued. You can then reorder the data, based on the AXI read ID of the transaction. This parameter applies to cases with multiple AXI transaction IDs. By using different AXI read/write IDs, you allow the HBM2 controller to reorder transactions for better efficiency. If you use the same AXI ID for all transactions, the controller issues the commands to memory in the order in which they arrive; in this instance, you need not enable the reorder buffer. |

| Enable AXI interface throttling based on temperature | Enables temperature-based throttling for this channel. You can specify the threshold temperature and throttling ratio on the General tab. Enables AXI thermal throttling for the specific HBM2 controller. The parameter that sets the trigger temperature for thermal throttling resides on the General tab. When the temperature of the HBM2 stack reaches the threshold temperature for HBM2 throttling as set on the General tab, the HBM2 controller begins to throttle user requests. |

| Address reordering | Describes the mapping of AXI address to HBM address. Specifies the pattern for mapping from the AXI interface to the HBM2 memory device. By choosing the right address reordering configuration, you help to improve the efficiency of accesses to the HBM2 memory device, based on user traffic pattern. The HBMC supports three types of address reordering: Address order (32B access: pseudo-BL8 disabled): SID-BG-BANK-ROW-COL[5:1] SID-ROW-BANK-COL[5:1]-BG ROW-SID-BANK-COL[5:1]-BG COL[0]=0 Address order (64B access (pseudo-BL8 enabled): SID-BG-BANK-ROW-COL[5:1]

SID-ROW-BANK-COL[5:2]-BG-COL[1]

ROW-SID-BANK-COL[5:2]-BG-COL[1]

COL[1:0] = {00})

SID applies only to the 8GB/8H HBM2 devices and is not available for 4GB/4H devices.

Note: The SID-BG-BANK-ROW-COL[5:1] address order limits HBM throughput when memory accesses are sequential, and also affects random access throughput in pseudo-BL8 mode.

|

| User Read Auto-Precharge Policy | Describes the policy for determining whether to issue auto-precharge. FORCED indicates that the controller follows the user auto-precharge request exactly. HINT indicates that the controller may override the auto-precharge request by disabling it when a page hit is detected (that is, if it receives two commands, one with auto-precharge and one without auto-precharge to the same page, the controller changes auto-precharge for the first to 0 so that the second can access the page without reopening it). You can issue the request to precharge together with the read command, through the axi_x_y_aruser input, where x denotes the HBM2 channel number (0-7) and y denotes the HBM2 Pseudo Channel number (0/1). You can choose between two values for this parameter:

|

| User Write Auto-Precharge Policy | Describes the policy for determining whether to issue auto-precharge. FORCED indicates that the controller follows the user auto-precharge request exactly. HINT indicates that the controller may override the auto-precharge request by disabling it when a page hit is detected (that is, if it receives two commands, one with auto-precharge and one without auto-precharge to the same page, the controller changes auto-precharge for the first to 0 so that the second can access the page without reopening it). You can issue a precharge request together with the write command, through the axi_x_y_awuser input, where x denotes the HBM2 channel number (0-7) and y denotes the HBM2 Pseudo Channel number (0/1). You can choose between two values for this parameter:

|

| Power Down Enable | Causes the controller to power down when idle. |

| Refresh mode | Specifies the method of controlling refreshes to the high bandwidth memory. User refresh modes are initiated with an access on the Advanced Peripheral Bus (APB). You can choose one of three values for this parameter:

|

| Enable AXI Burst length of more than 2 | When this option is enabled, the HBM2 IP supports sequential burst transactions at the AXI Interface. This feature is applicable to AXI channel without switch enabled only. This option enables you to use the AWLEN/ARLEN inputs of the AXI interface and issue sequential burst traffic. The burst size is defined by by the value provided by AWLEN/ARLEN in the burst length 4 mode. You can select this option only when using the BL4 mode at the HBM2 DRAM. |

| AXI Maximum burst length | Maximum of 256 is supported when the enable more than 2 Burst length option is enabled. If the option is disabled, a default value of 1 is set. The maximum burst length value determines the width of the awid/arid. Refer to the AXI Interface Signals section for more details. |

| Enable Pseudo BL8 for performance | If enabled, data access granularity is 64B (64 bits per Pseudo-Channel at BL8) which can achieve greater efficiency. Otherwise data access granularity is 32B (64 bits per Pseudo-Channel at BL4). The controller sets the memory transactions burst length based on this setting and ignores the input provided on the user-driven axi_awsize and axi_arsize signals on the AXI interface. |

| Data width per Pseudo-Channel | Data width per Pseudo Channel. The available data widths are: 256 bits - This refers to 256-bit data transfers at the AXI interface. ECC or write data mask option is available in this data width mode only. 288 bits - This refers to 288-bit data transfers at the AXI interface. ECC or write data mask option is not available in this mode. You must implement your own ECC logic when choosing this data width option. |

| Memory channel ECC generation and checking/correction | Memory Channel ECC generation and checking / correction. The HBM2 controller supports single-bit error correction and double-bit error detection. This feature is available only when you select the 256-bit data width mode. The controller does not support write data mask in ECC generation mode. |

| Write data mask enable | Enables the write data mask (DM) input to the HBM2 DRAM. When you use the DM pins, you cannot use ECC. This feature is available only when you select the 256-bit AXI data width mode. |