Intel® Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000

ID

683040

Date

6/14/2021

Public

1. About this Document

2. System Requirements

3. Hardware Installation

4. Installing the OPAE Software

5. OPAE Tools

6. Sample Test: Native Loopback

7. Installing the Intel XL710 Driver

8. Configuring Ethernet Interfaces

9. Testing Network Loopback Using Data Plane Development Kit (DPDK)

10. Graceful Shutdown

11. Single Event Upset (SEU)

12. Document Revision History for Intel Acceleration Stack User Guide: Intel® FPGA PAC N3000

A. Troubleshooting

B. Upgrade your Intel® FPGA PAC N3000 with Production Version of BMC and Intel® Arria® 10 Image

C. Configure the 4.19 Kernel

D. fpgabist Sample Output

8.4. Get Link Status and Statistics

To retrieve the line side link status, use the Linux ethtool and get link statistics using OPAE fpgastats command:

$ ethtool npacf0g0l0Settings for npacf0g0l0:

Link detected: yes

$ ethtool -S npacf0g0l1

This command lists FPGA Ethernet counters

$ ethtool -S p7p1

This command lists XL710 Ethernet counters

Note: The Ethernet links between the FPGA and XL710 controllers is always up when the FPGA is being programmed.

The OPAE fpgastats command lists all FPGA Ethernet MAC counters on the Intel® FPGA PAC N3000 specified by bus number. The fpgastats command is useful for detecting packet drops inside the FPGA because it provides both Ethernet wrapper 0 and 1 in an easily read format.

$ sudo fpgastats [-h] [--segment SEGMENT] [--bus BUS] [--device DEVICE] [--function FUNCTION] [--clear] [--debug]

optional arguments:

-h, --help show this help message and exit

--segment SEGMENT, -S SEGMENT

Segment number of PCIe device

--bus BUS, -B BUS Bus number of PCIe device

--device DEVICE, -D DEVICE

Device number of PCIe device

--function FUNCTION, -F FUNCTION

Function number of PCIe device

--clear, -c Clear statistics

--debug, -d Output debug information

$ sudo fpgastats -B 0x8a -c

Note: The XL710 controller does not support the OPAE fpgastats command.

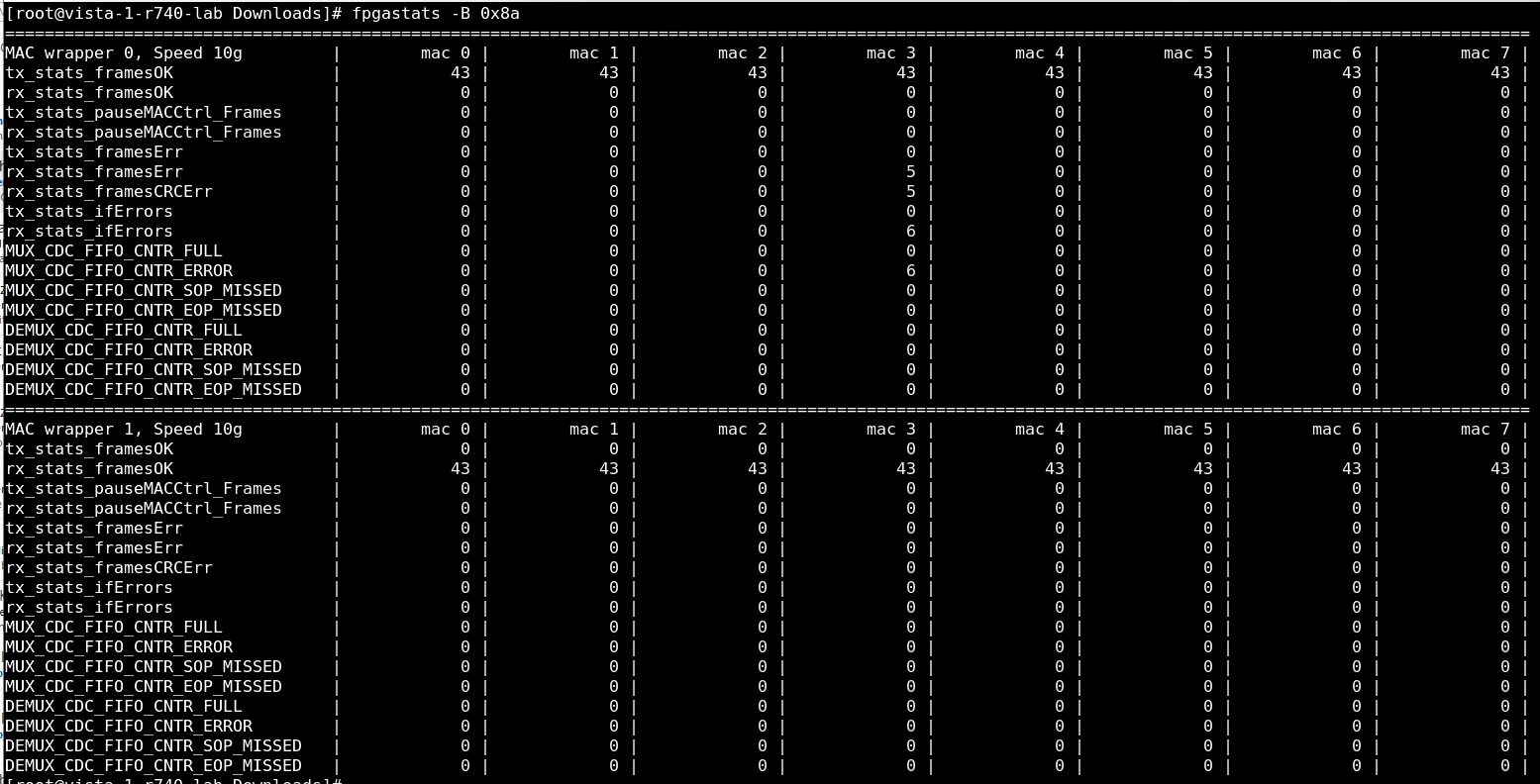

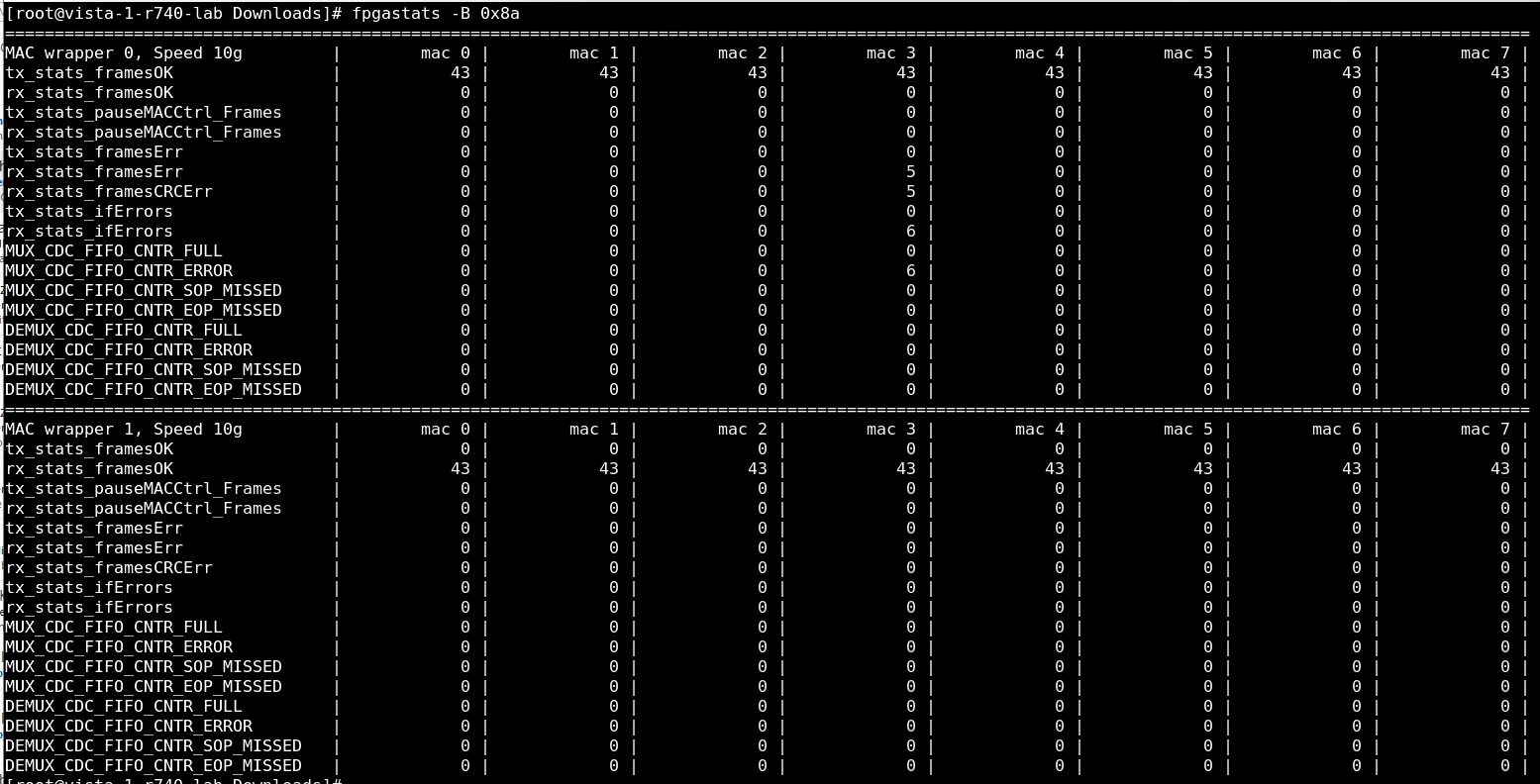

Figure 16. Sample Output

| Name | Description |

|---|---|

| tx_stats_* | Refer to Low Latency Ethernet 10G MAC Intel FPGA IP User Guide. |

| rx_stats_* | |

| CNTR_TX_* | Refer to 25G Ethernet Intel Arria 10 FPGA IP User Guide or Low Latency 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function User Guide. |

| CNTR_RX_* | |

| MUX_CDC_FIFO_CNTR_FULL | Drop counter on MUX. Increments when mux_cdc_fifo is full and there is no space for current packet. |

| MUX_CDC_FIFO_CNTR_ERROR | Counts packets marked with error on RX Avalon® streaming interface of MUX. |

| MUX_CDC_FIFO_CNTR_SOP_MISSED | Counts missed SOP on RX Avalon® streaming interface of MUX. |

| MUX_CDC_FIFO_CNTR_EOP_MISSED | Counts missed EOP on RX Avalon® streaming interface of MUX. |

| DEMUX_CDC_FIFO_CNTR_FULL | Drop counter on DEMUX. Increments when demux_cdc_fifo is full and there are no space for current packet. |

| DEMUX_CDC_FIFO_CNTR_ERROR | Counts packets marked with error on RX Avalon® streaming interface of DEMUX. |

| DEMUX_CDC_FIFO_CNTR_SOP_MISSED | Counts missed SOP on RX Avalon® streaming interface of DEMUX |

| DEMUX_CDC_FIFO_CNTR_EOP_MISSED | Counts missed EOP on RX Avalon® streaming interface of DEMUX |