3.3. PTA - Hierarchical Design Editor

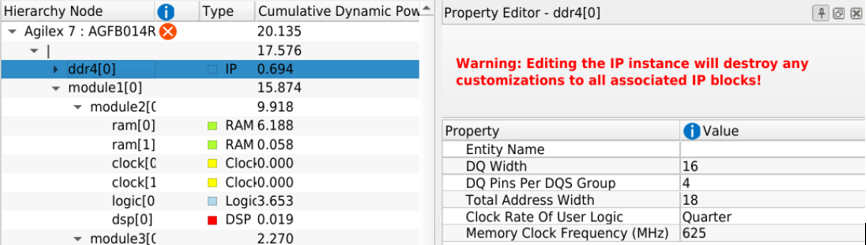

The Hierarchical Design Editor tab in the Data Entry pane displays the dynamic power consumption for each resource in the hierarchy of the design. The Hierarchical Design Editor allows you to enter and modify hierarchy names, add and remove resource entries, and delete unneeded hierarchy levels.

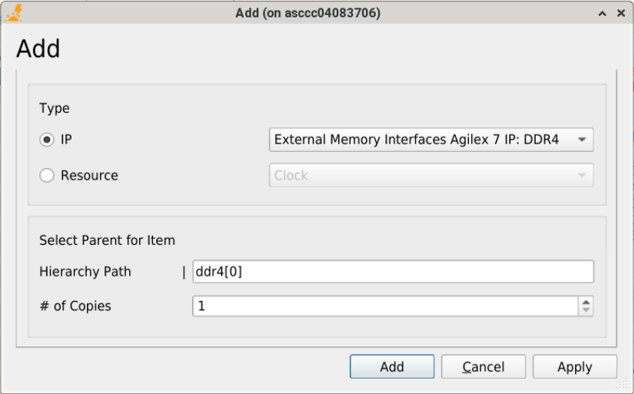

Add Dialog

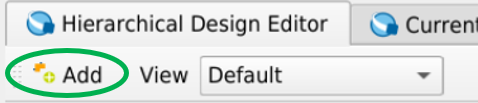

The Hierarchical Design Editor tab has an Add dialog box which you can use to add resources or IP to your design. Click the Add button to open the dialog box.

| Resource Type | Description |

|---|---|

| Clock | Allows you to specify the properties of the clock networks of separate clock domains in your design. Specify the clock domain name, clock frequency, total fan-out, and other properties about the clocks in your design. |

| Crypto | Allows you to specify the properties of crypto resources and their settings for all entities in your design, such as the entity name, full hierarchy name, and number of instances. (Agilex FPGA portfolio devices with crypto blocks only). |

| DSP | Allows you to specify the properties of DSP design entities. Specify the DSP configuration, clock frequency, toggle percentage, and register usage for the DSPs in your design. |

| HBM | Allows you to specify the properties of high-bandwidth memory (HBM) entities in your design. (Devices with HBM blocks only). |

| I/O | Allows you to specify the properties of design entities using general-purpose I/O pins. This resource type does not apply to transceiver I/O pins. Specify I/O standard, input termination, current strength or output termination, data rate, clock frequency, output enable static probability, and capacitive load for the I/O in your design. |

| Logic | Allows you to specify the properties of logic resources for all entities in your design. |

| NOC | The dynamic power consumed by the network-on-chip system (NoC). (Devices with NOC only.) |

| PLL | Allows you to specify the properties of one or more PLLs in your design. |

| RAM | Allows you to specify the properties of design entities implemented in RAM blocks. Specify the RAM type, data width, RAM depth (if applicable), RAM mode, and port parameters for these entities in your design. |

| Transceiver | Allows you to specify the transceiver resources and their settings for your design entities. |

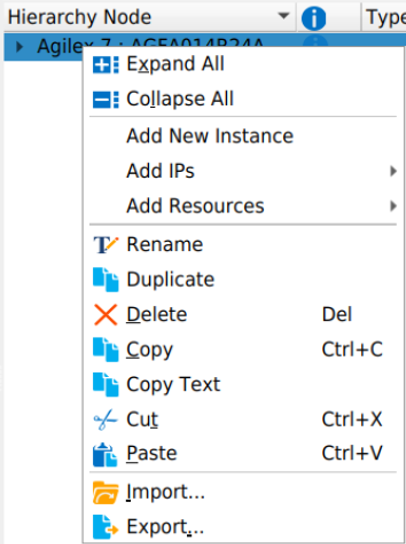

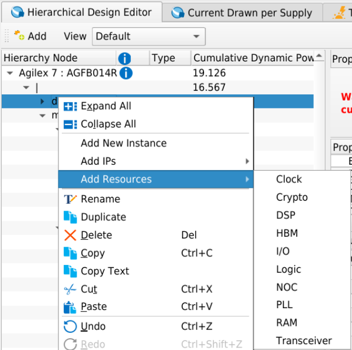

Context Menu

| Button or Control | Description |

|---|---|

| Expand All | Expands all hierarchy at current level and below. |

| Collapse All | Collapses all hierarchy at current level and below. |

| Add New Instance | Adds an instance to the currently selected level. |

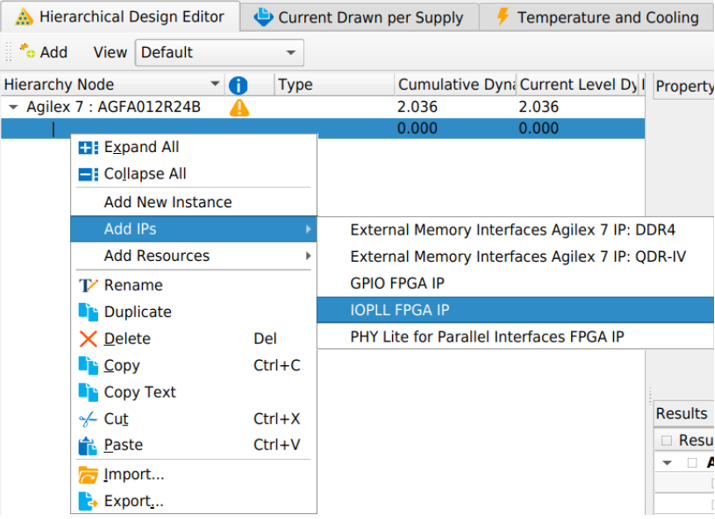

| Add IPs | Adds an IP selected in the associated submenu to the design at the currently selected level. |

| Add Resources | Adds a resource selected in the associated submenu to the design at the currently selected level. |

| Rename | Rename the currently selected item (Only available for instances). |

| Duplicate | Duplicates the currently selected level of hierarchy or resource. |

| Delete | Deletes the currently selected level of hierarchy or resource. |

| Copy | Copies the currently selected level of hierarchy or resource to the clipboard. |

| Copy Text | Copies the name of the selected item to the clipboard. For resources also copies the resource type, and power figures. |

| Cut | Copies the currently selected level of hierarchy or resource to the clipboard and marks it for deletion on paste. |

| Paste | Pastes the previously copied level of hierarchy or resource into the current location. |

| Import | Opens the Import Dialog dialog box to import the resources in a newly selected .pta, .ptc, .qpta, or qptc file to the selected level of hierarchy. |

| Export | Exports the currently selected item and those below it in hierarchy to a .pta file. |

In the Hierarchical Design Editor, you enter information about your design that informs the power estimation calculations. Entry is at the hierarchal level. The Power and Thermal Analyzer (PTA) uses the values that you specify on the resource entries to calculate the power consumption and other data.

Adding IPs

The Power and Thermal Analyzer supports a selection of IPs to add to the design. The IPs available depend on the currently selected device.

You can edit parameters of the selected IP in the Property Editor panel after addition: