External Memory Interfaces Agilex™ 7 M-Series FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

- 4.1.2. s0_axi4_clock_out for Agilex 7 M-Series External Memory Interfaces (EMIF) IP - DDR4 Component

- 4.3.2. s0_axi4_clock_out for Agilex 7 M-Series External Memory Interfaces (EMIF) IP - DDR5 Component

12.1.6.1.1. Example 4: Sending ECC_INJECT_ERROR Using the Mailbox and Reading ECC Error Status, ECC Error Buffer Registers

The values in this example are for illustrative purposes and are obtained from an EMIF example design using LPDDR4 1ch x32 component, implement on the Agilex™ 5 FPGA E-Series 065B Premium Development Kit.

For a 1ch x32 LPDDR4 component design, the interface uses the Primary MC of Primary IO96B, hence the CMD_TARGET_IP_TYPE is 0x1. The CMD_TARGET_IP_INSTANCE defaults to 0 in the design example generated by the Quartus® Prime software. The design example is generated with In-Line ECC enabled.

The following table illustrates the construction of the data to be written to the CMD_REQ register for this request:

| CMD_REQ [31:29]: CMD_TARGET_IP_TYPE | CMD_REQ [28:24]: CMD_TARGET_IP_INSTANCE_ID | CMD_REQ [23:16]: CMD_TYPE | CMD_REQ [15:0]: CMD_OPCODE | CMD_REQ [31:0]: |

|---|---|---|---|---|

| 0x1 | 0x0 | 0x04 | 0x109 | 0x20040109 |

Flagging error on specific memory address using JAMB/AXI-Lite

Prerequisites:

- Ensure the design generated with ECC enabled. If you modify the ECC enable status via a mailbox command, verify ECC is enabled by reading the ECC_ENABLE_INTF0/1 read-only status register.

- Ensure the design is generated with a non-infinite Traffic Generator Program so that write traffic to a known address can be compiled and executed in user mode. Follow these steps for compiling traffic program to perform single write and read on a specific memory address:

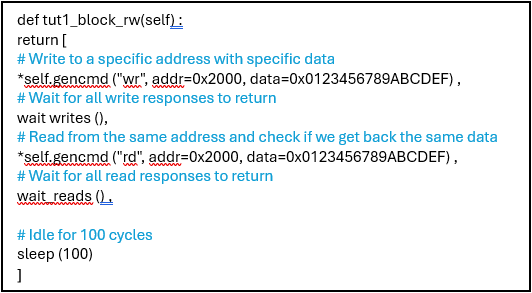

- Open the traffic_patterns.py file from the <project directory>/qii/hydra_sw folder and navigate to a function called tut1_block_rw.

- Specify the address at “addr” parameter as shown in example below and save the file.

(Comment or remove all other commands within this function, except for the ones performing single write to a specific address and reading from the same address)

- Execute the command to compile the traffic program:

quartus_py main.py --ipdir=<project directory>/qii/ --prog=tut1_block_rw

- The <project directory>/qii/hydra_sw/bin folder is updated from the command execution above. Copy the generated /bin folder to <project_directory>/qii. The traffic program is now ready to perform a single write to a known address and read from the same address.

Execution:

- Write to CMD_PARAM_0(address=0x 0x5000438) register the syndrome to program the ECC_XOR_CHECK_BITS parameter(write_data=0xf4).

Note: 0xf4 will update the check bits and write to memory as single bit correctable error on bit [0]. Refer to Table 283 for ECC syndrome codes.

- Write the CMD_REQ(address=0x500043C) with write_data=0x20040109.

- Read from CMD_RESPONSE_STATUS(address=0x500_045c) until you get the STATUS_COMMAND_RESPONSE_READY (Bit 0 of CMD_RESPONSE_STATUS register) equals 1.

- Clear the STATUS_COMMAND_RESPONSE_READY (Bit 0 of CMD_RESPONSE_STATUS register) Perform a Read-Modify-Write operation:

- Read from CMD_RESPONSE_STATUS register.

- Write_Data = Data in (a) & 0xffff_fffe (Change only bit 0).

- Write to address = 0x500_045c data= write_data from (b).

- Run traffic generator.

system-console --script=<path to testengine_library.tcl> --sof=<path to sof_file> --update=1 --n-loops=1

You should observe that the traffic has failed. - Read ECC_ERR_COUNTER from ECC_ERR_STATUS(address= 0x5000300) read-only register (bit 0 to bit 15). The expected read_data=0x0000_0001; indicates that 1 error encountered.

- Read ECC Error Buffer Entry 0(R1 address= 0x5000310 , R2 address= 0x5000314).

The expected read_data from R1= 0x00400000

IP_TYPE [22:24] : 1 ==> Primary MC of Primary IO96B INSTANCE_ID [21:17] : 0 ECC_ERR_SOURCE_ID [16:10] : 0 ECC_ERR_TYPE [9:6] : 0 ==> Single-bit error ECC_ERR_ADDR_UPPER [5:0] : 0 ==> 0x0

The expected read_data from R2= 0x00002000.

ECC_ERR_ADDR_LOWER[31:0]: 8192 ==> 0x2000

- Repeat the above steps and observe the ECC_ERR_COUNTER increase accordingly. Read the respective ECC Error Buffer Entry (0 to 15) based on the number of ECC events.

When the ECC error buffer reaches its full capacity of 16 entries, proceed to the next steps to check ECC_ERR_OVERFLOW status.

- Read ECC_ERR_OVERFLOW from ECC_ERR_STATUS (address= 0x5000300) read-only register (bit 16 to bit 31).

The expected read_data=0x0001; indicates that single-bit error overflow occurred.

Clear the ECC error buffer, reset the ECC error counter and reset overflow register

It is not required to write to the CMD_PARAM_* register as this OPCODE does not require any cmd_param.

The following table illustrates the construction of the data to be written to the CMD_REQ register for this request using the same design as the previous example targeting an Agilex™ 5 FPGA E-Series 065B Premium Development Kit:

| CMD_REQ [31:29]: CMD_TARGET_IP_TYPE | CMD_REQ [28:24]: CMD_TARGET_IP_INSTANCE_ID | CMD_REQ [23:16]: CMD_TYPE | CMD_REQ [15:0]: CMD_OPCODE | CMD_REQ [31:0]: |

|---|---|---|---|---|

| 0x1 | 0x0 | 0x04 | 0x110 | 0x20040110 |

- Write the CMD_REQ(address=0x500043C) with write_data=0x20040110.

- Read from CMD_RESPONSE_STATUS(address=0x500_045c) until you get the STATUS_COMMAND_RESPONSE_READY (Bit 0 of CMD_RESPONSE_STATUS register) equals 1.

- Clear the STATUS_COMMAND_RESPONSE_READY (Bit 0 of CMD_RESPONSE_STATUS register) Perform a Read-Modify-Write operation:

- Read from CMD_RESPONSE_STATUS register.

- Write_Data = Data in (a) & 0xffff_fffe (Change only bit 0).

- Write to address = 0x500_045c data= write_data from (b).

- Reading ECC_ERR_STATUS (address= 0x5000300) and ECC Error Buffer Entry (0 to 15) should return 0, indicates that the previous data cleared/reset successfully.