4.3. 4G Turbo-V Signals and Interfaces

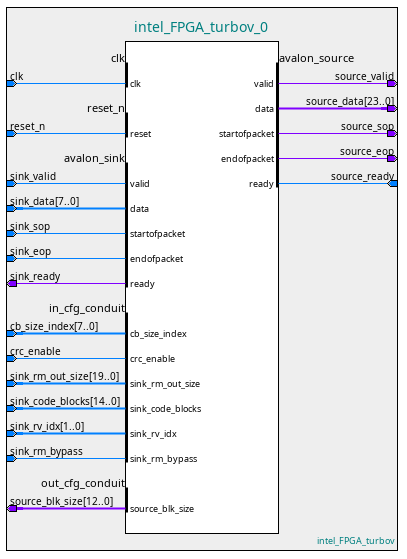

Downlink Accelerator

Figure 10. Downlink Accelerator Interfaces

| Signal Name | Direction | Bit Width | Description |

|---|---|---|---|

| clk | Input | 1 | Clock input. All Turbo-V IP interface signals are synchronous to this clock. |

| reset_n | Input | 1 | Resets the internal logic of whole IP. |

| sink_valid | Input | 1 | Asserted when data at sink_data is valid. |

| sink_data | Input | 8 | Typically carries the bulk of the information being transferred. |

| sink_sop | Input | 1 | Indicates the start of an incoming packet |

| sink_eop | Input | 1 | Indicates the end of an incoming packet |

| sink_ready | Output | 1 | Indicates when the IP can accept data |

| crc_enable | Input | 1 | Enables the CRC block |

| cb_size_index | Input | 8 | Input code block size K |

| sink_rm_out_size | Input | 20 | Rate matcher output block size, corresponding to E. |

| sink_code_blocks | Input | 15 | Soft buffer size for current code block Ncb |

| sink_rv_idx | Input | 2 | Redundancy version index (0,1,2 or 3) |

| sink_rm_bypass | Input | 1 | Enables bypass mode in the rate matcher |

| source_valid | Output | 1 | Asserted by the IP when there is valid data to output. |

| source_data | Output | 24 | Carries the bulk of the information transferred. This information is available where valid is asserted. |

| source_sop | Output | 1 | Indicates the beginning of a packet. |

| source_eop | Output | 1 | Indicates the end of a packet. |

| source_ready | Input | 1 | Data reception is valid where the ready signal is asserted. |

| Source_blk_size | Output | 13 | Output code block size K |

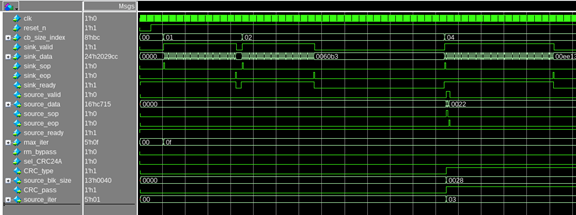

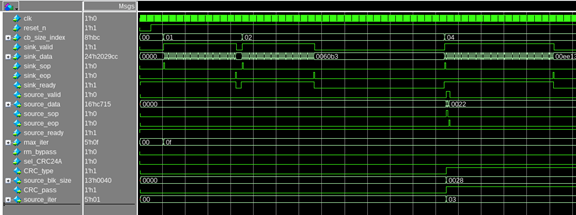

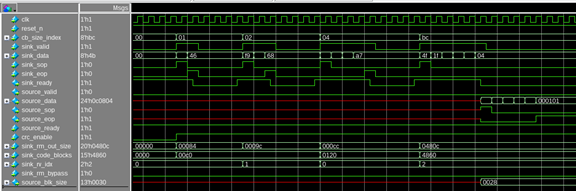

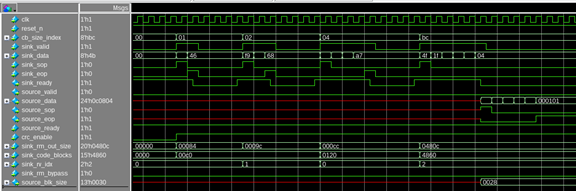

Figure 11. Downlink Signals

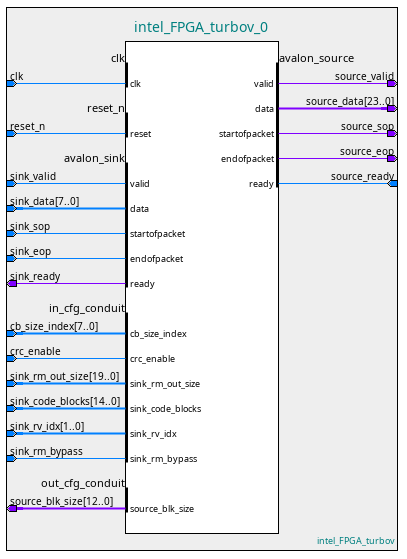

Uplink Accelerator

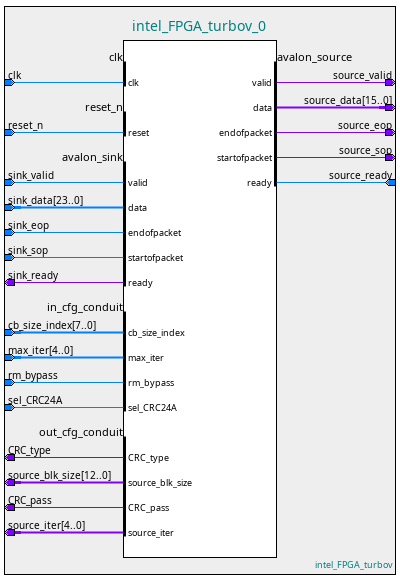

Figure 12. Uplink Accelerator Interfaces

| Signal | Direction | Bit Width | Description |

|---|---|---|---|

| clk | Input | 1 | Clock input. All Turbo-V IP interface signals are synchronous to this clock. |

| reset_n | Input | 1 | Reset of input clock signal |

| sink_valid | Input | 1 | Avalon streaming input valid |

| sink_data | Input | 24 | Avalon streaming input data |

| sink_sop | Input | 1 | Avalon streaming input start of packet |

| sink_eop | Input | 1 | Avalon streaming input end of packet |

| sink_ready | Input | 1 | Avalon streaming input ready |

| cb_size_index | Input | 8 | Block size index |

| max_iteration | Input | 5 | Specify the maximum number of half-iterations |

| rm_bypass | Input | 1 | Enables bypass mode |

| sel_CRC24A | Input | 1 | Specify the type of CRC that you need for the current data block: • 0: CRC24B • 1: CRC24A |

| source_valid | Output | 1 | Avalon streaming output valid |

| source_data | Output | 16 | Avalon streaming output data |

| source_sop | Output | 1 | Avalon streaming output start of packet |

| source_eop | Output | 1 | Avalon streaming output end of packet |

| source_ready | Output | 1 | Avalon streaming output ready |

| CRC_type | Output | 1 | Indicates the type of CRC that was used for the current data block: • 0: CRC24A • 1: CRC24B

|

| source_blk_size | Output | 13 | Specifies the outgoing block size |

| CRC_pass | Output | 1 | Indicates whether CRC was successful: • 0: Fail • 1: Pass |

| source_iter | Output | 5 | Shows the number of half iterations after which the Turbo decoder stops processing the current data block. |

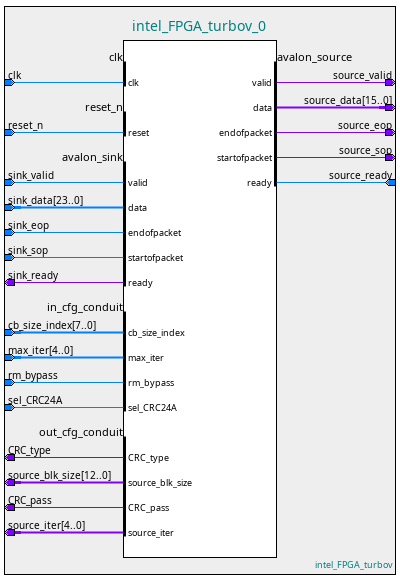

Figure 13. Uplink Signals