Multi Channel DMA for PCI Express* Intel® FPGA IP Design Example User Guide

ID

683517

Date

12/01/2021

Public

A newer version of this document is available. Customers should click here to go to the newest version.

2.5.1. Simulation Results

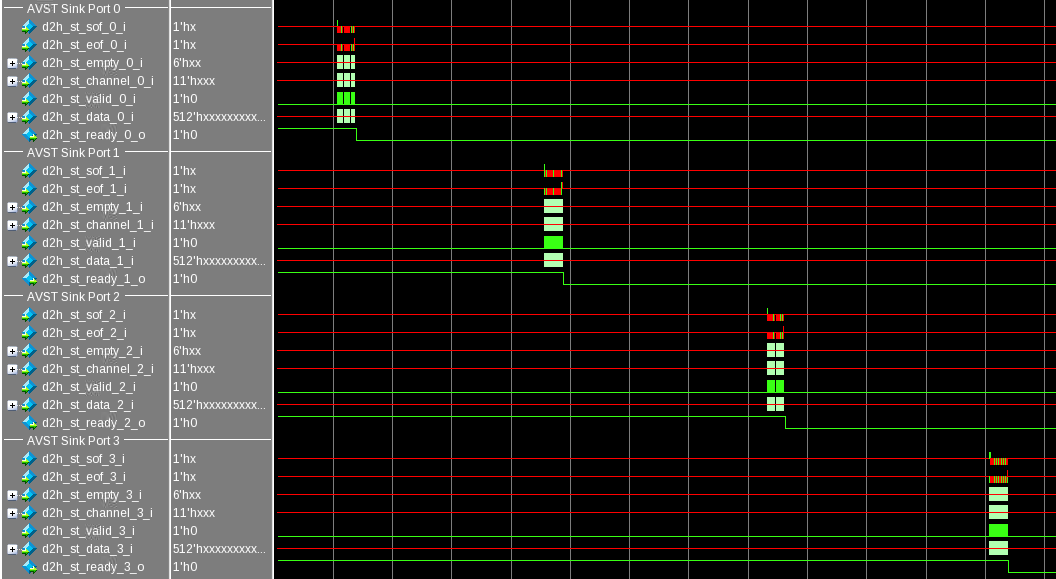

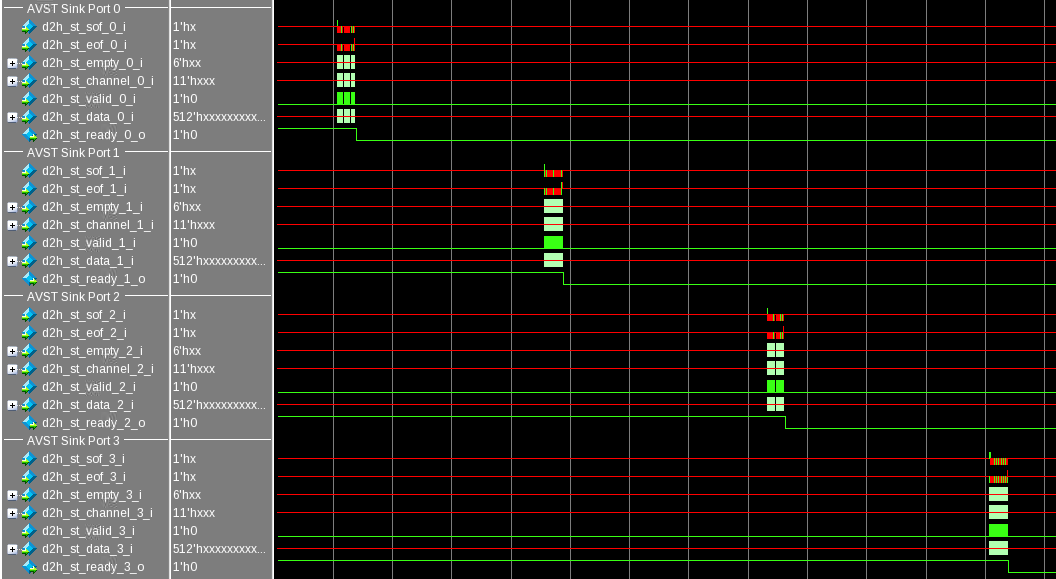

Figure 23. Simulation Log

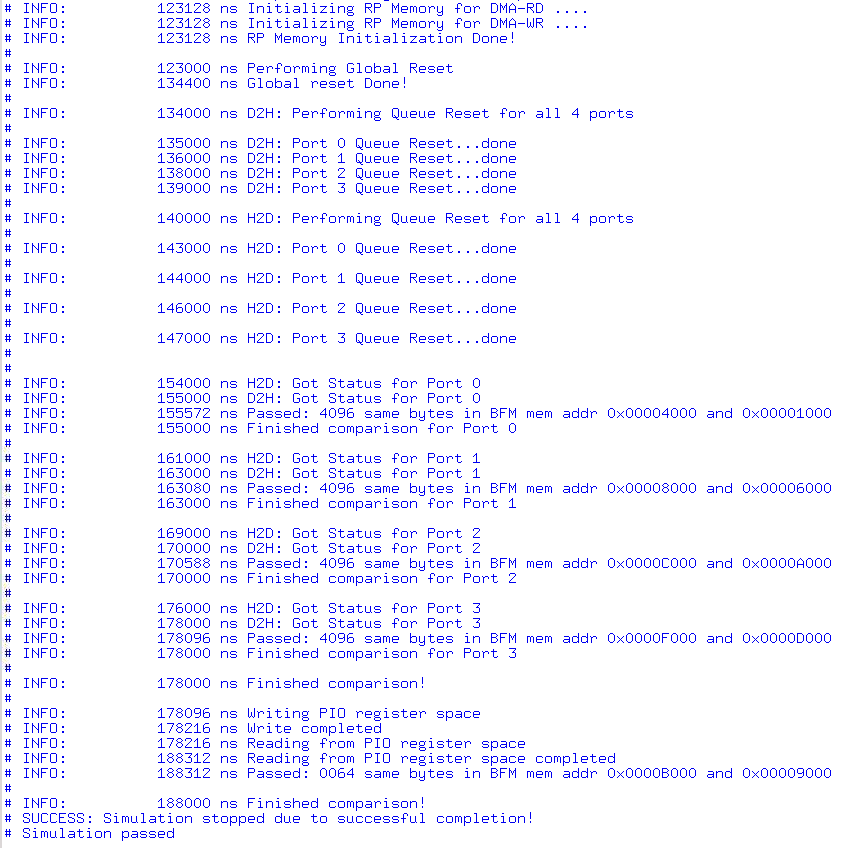

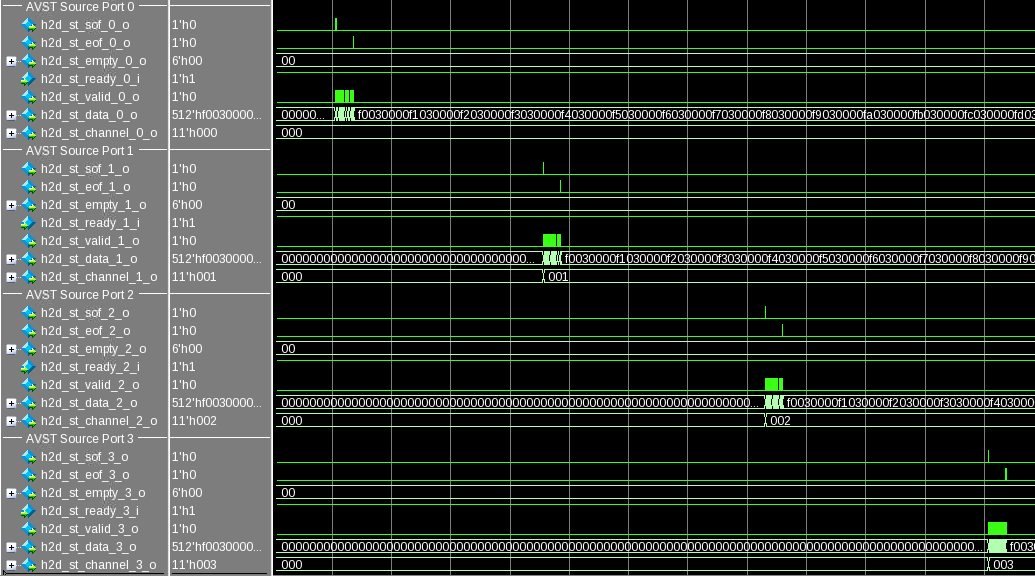

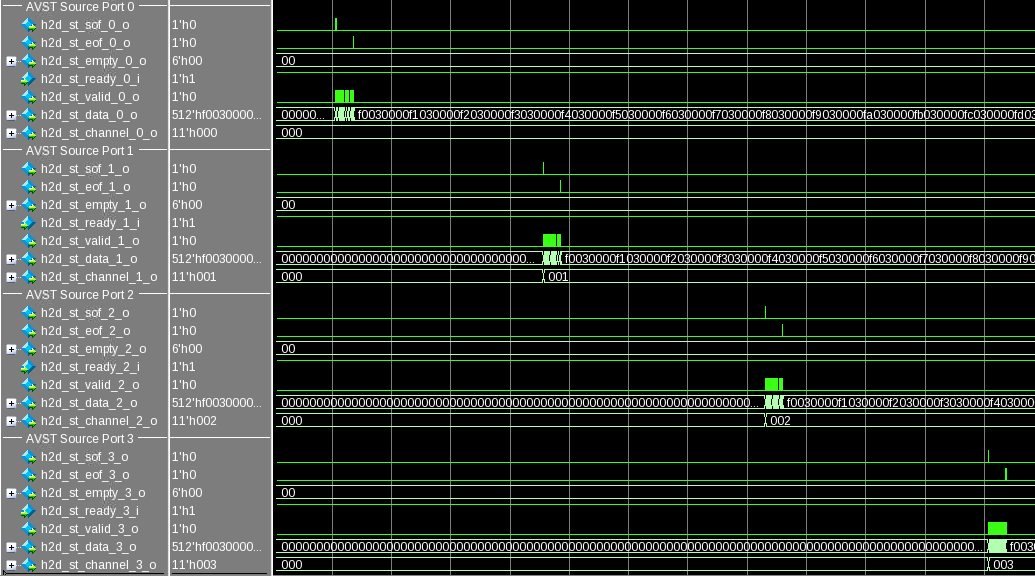

Figure 24. H2D Simulation Waveform

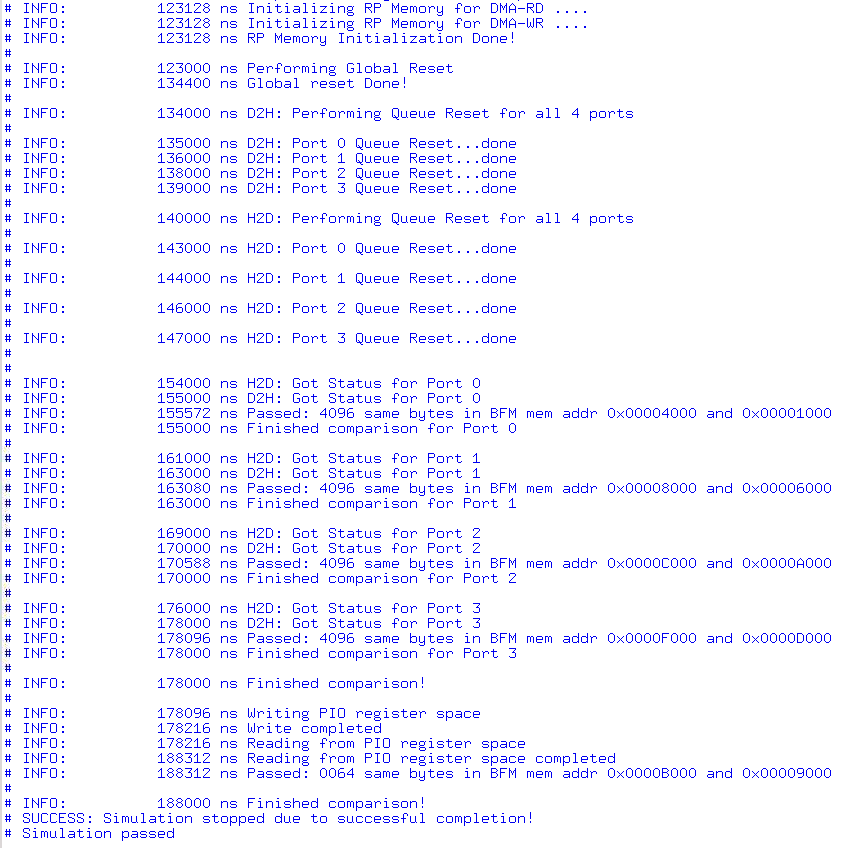

Figure 25. D2H Simulation Waveform