AN 793: Intel® Arria® 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design

Video and Image Processing Block

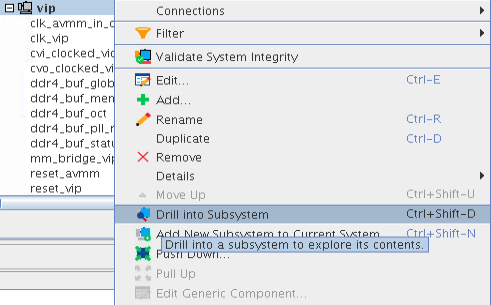

The VIP block receives video data from the DisplayPort Sink, processes and transmits the processed data to the DisplayPort Source. To navigate to the VIP subsystem through dp_core.qsys, right click vip, and select Drill into subsystem.

- Clocked Video Input II IP core: Converts the DisplayPort Sink video output format to Avalon-ST video protocol

- Frame Buffer II IP core: Handles mismatch in RX and TX video data rate through triple-buffering

- Mixer II IP core: Overlays the buffered image on top of the background color bar

- Clocked Video Output II IP core: Converts the Avalon-ST video protocol to the DisplayPort Source video input format

| IP Core | Parameter | Value |

|---|---|---|

| Clocked Video Input II |

Bits per pixel per color plane |

10 |

| Number of color planes | 3 | |

| Number of pixels in parallel |

4 |

|

| Use control port |

Off |

|

| Frame Buffer II |

Maximum frame width |

3840 |

| Maximum frame height | 2160 | |

| Bits per pixel per color plane |

10 |

|

| Number of color planes | 3 | |

| Pixels in parallel |

4 |

|

| Avalon-MM master (s) local ports width |

512 |

|

| AV-MM burst target write |

64 |

|

| AV-MM burst target read |

64 |

|

| Frame dropping |

On |

|

| Frame repeating |

On |

|

| Drop invalid frames |

On |

|

| Run-time writer control |

Off |

|

| Mixer II |

Maximum output frame width |

3840 |

| Maximum output frame height |

2160 |

|

| Bits per pixel per color plane |

10 |

|

| Number of pixels in parallel |

4 |

|

| Colorspace (used for background layer) | RGB | |

| Pattern | Color bars | |

| How user packets are handled | Discard all user packets received | |

| Clocked Video Output II |

Image width / Active pixels |

3840 |

| Image height / Active lines |

2160 |

|

| Bits per pixel per color plane |

10 |

|

| Number of color planes | 3 | |

| Number of pixels in parallel |

4 |

|

| Separate syncs only - Frame/ Field 1 Horizontal sync |

32 |

|

| Separate syncs only - Frame/ Field 1 Horizontal front porch |

48 |

|

| Separate syncs only - Frame/ Field 1 Horizontal back porch |

80 |

|

| Separate syncs only - Frame/ Field 1 Vertical sync |

5 |

|

| Separate syncs only - Frame/ Field 1 Vertical front porch |

3 |

|

| Separate syncs only - Frame/ Field 1 Vertical back porch |

54 |

|

| Pixel FIFO size |

3840 |

|

| FIFO level at which to start output |

3839 |

|

| Use control port |

Off |