GTS AXI Multichannel DMA IP for PCI Express* User Guide

A.1.6. Root Port Address Translation Table Enablement

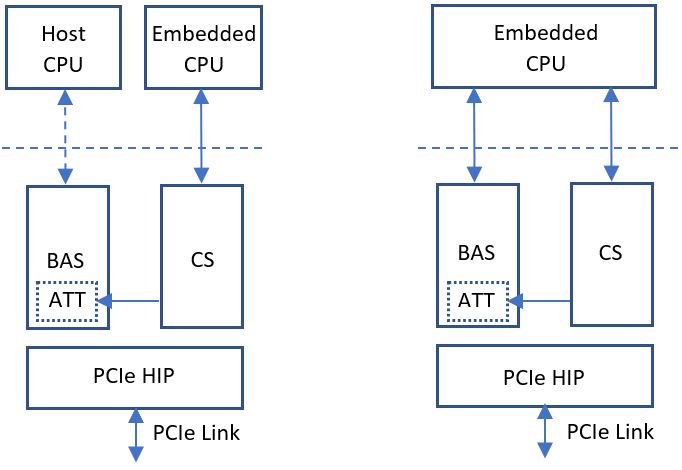

The Root Port Address Translation Table (ATT) translates the address driven by the AXI-MM Manager connected to the Bursting Slave (BAS). This allows the AXI-MM Manager interface with a smaller address bus to access a larger address space. For example, if the embedded CPU with the smaller address bus is the AXI-MM Manager, ATT enables the embedded CPU to access the entire 64-bit PCIe address space. If the host CPU is the master, ATT can be used to translate the host address bus. The following figure shows example use cases.

The IP provides the following parameters in the IP Parameter Editor (MCDMA Settings) that allow you to select the address mapping when you enable ATT.

- ATT Table Address Width (1-9): Sets the depth of the ATT. Depth is equal to 2 to the power of the number entered.

- ATT Window Address Width (10-63): Sets the number of BAS address bits to be used directly.

When address mapping is disabled, the AXI-MM subordinate address is used as-is in the resulting PCIe TLPs. When address mapping is enabled, burst of transactions on the AXI-MM subordinate interfaces must not cross address mapping page boundaries. This requirement means (address + 32 * burst count) <= (page base address + page size). Host software is expected to guarantee this in the Root Port mode. The BAS/CS does not have any mechanism to report the error if this requirement is violated.

When address mapping is enabled, the AXI-MM lower-order address bits are passed through to the PCIe TLPs unchanged and are ignored in the address mapping table. The number of lower-order address bits that are passed through defines the size of the page and is set by the ATT Window Address Width parameter in the IP Parameter Editor. If bits [63:32] of the resulting PCIe address are zero, TLPs with 32-bit wide addresses are created as required by the PCI Express standard.

For example, if you define 16 address mapping windows of 64 KB each at configuration time and program the local CS addresses 0x3018 and 0x301C with 0x56780000 and 0x00012340 respectively, a read or write transaction to address 0x39AB0 on the bursting AXI-MM subordinate interface gets transformed into a memory read or write TLP accessing PCIe address 0x0001234056789AB0.

In the figure below, the ATT depth is 64. This is set by ATT Table Address Width = 6 (26= 64 deep). The address pass-through width is 16. This is set by ATT Window Address Width = 16. This means BAS forwards the lower 16-bit address as is. The upper 6 bits are used to select the ATT entry. In the example, the ATT entry selection is 0x03.

The Flow is:

- The host software is expected to program all the ATT registers in the CS for all enabled locations.

- When the AXI-MM transaction is received by BAS, it detects the address being 32-bit or 64-bit and enables the translation logic in CS as shown above. If the address translation gets enabled, the BAS logic retrieves the translated data from the ATT table as shown in the figure above.