External Memory Interfaces (EMIF) IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs

ID

817394

Date

4/01/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the External Memory Interfaces Agilex™ 5 FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 5 FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 5 FPGA IP

4. Document Revision History for External Memory Interfaces (EMIF) IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Agilex™ 5 EMIF IP

2.7. Compiling the Agilex™ 5 EMIF Design Example

2.8. Generating the EMIF Design Example with the Performance Monitor

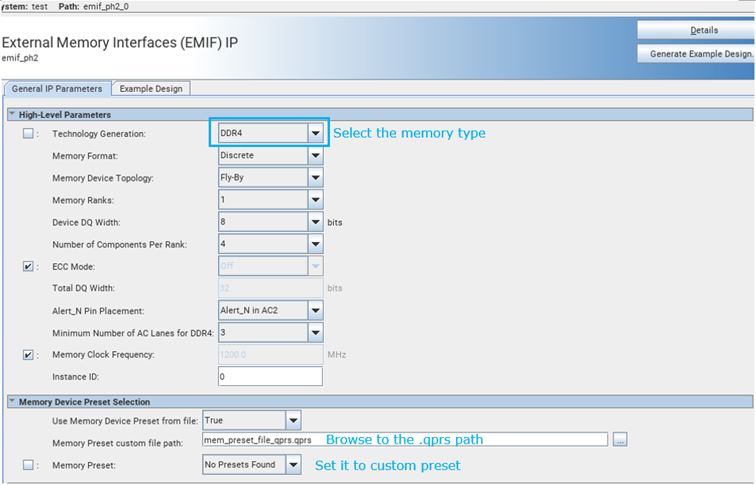

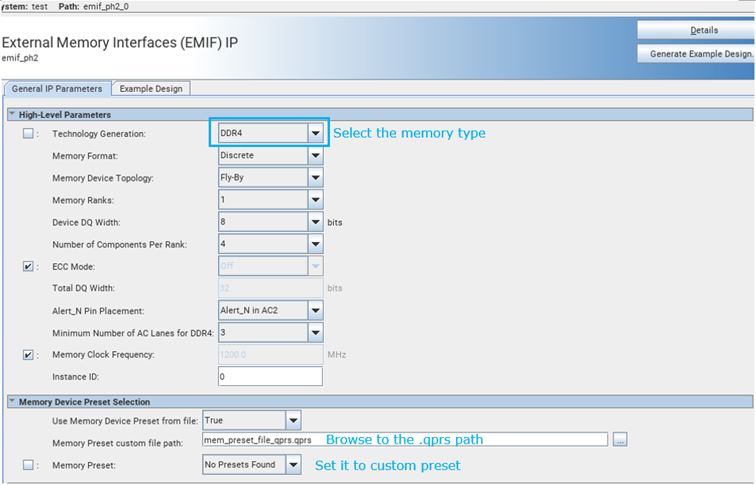

2.2.2. Using Custom Memory Device Presets from a File

If you want, you can use custom memory device presets that you have saved to a file previously.

To use memory device presets that you have saved previously, follow these steps:

- In the Memory Device Preset Selection group box of the External Memory Interfaces IP parameter editor, set Use Memory Device from File to True.

- In the Memory Preset Custom File Path field, select the required memory device presets file. (The presets file must have a .qprs file extension.)

- In the Memory Preset field, select Custom Preset.

Figure 20. Memory Device Preset Selection

Note:

If you are unable to find or select a custom presets file, it might be because your presets file fails to meet the following requirements:

- The device DQ width in the custom memory device presets file must match the selected device DQ width in the EMIF IP parameter editor.

- The clock frequency in the custom memory device presets file must match the clock frequency selected in the EMIF IP parameter editor.

- The custom memory presets file name must have a .qprs extension.

Note: For information on saving custom memory device presets to a file, refer to the Generating a Custom Memory Presets File topic for your memory protocol.