External Memory Interfaces (EMIF) IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs

ID

817394

Date

4/01/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the External Memory Interfaces Agilex™ 5 FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 5 FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 5 FPGA IP

4. Document Revision History for External Memory Interfaces (EMIF) IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Agilex™ 5 EMIF IP

2.7. Compiling the Agilex™ 5 EMIF Design Example

2.8. Generating the EMIF Design Example with the Performance Monitor

2.2. Generating and Configuring the EMIF IP

The following steps illustrate how to generate and configure the EMIF IP. This walkthrough creates a DDR4 interface, but the steps are similar for other protocols. (These steps follow the IP Catalog (standalone) flow; if you choose to use the Platform Designer (system) flow instead, the steps are similar.)

- In the IP Catalog window, select External Memory Interfaces IP. (If the IP Catalog window is not visible, select View > IP Catalog.)

Figure 17. IP Catalog

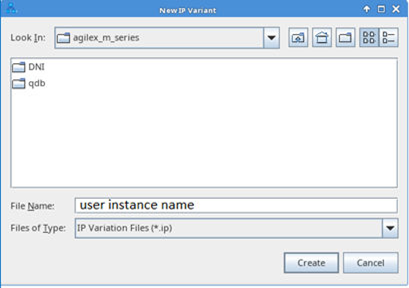

- In the IP Parameter Editor, provide an entity name for the EMIF IP (the name that you provide here becomes the file name for the IP) and specify a directory. Click Create.

Figure 18. Specifying a File name

- The parameter editor has multiple tabs where you must configure parameters to reflect your EMIF implementation.