F-Tile DisplayPort Intel® FPGA IP Design Example User Guide

ID

709308

Date

11/03/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

2.1. Intel Agilex® 7 F-Tile DisplayPort SST Parallel Loopback Design Features

2.2. Intel Agilex® 7 F-Tile DisplayPort SST TX-only Design Features

2.3. Intel Agilex® 7 F-Tile DisplayPort SST RX-only Design Features

2.4. Design Components

2.5. Clocking Scheme

2.6. Interface Signals and Parameters

2.7. Simulation Testbench

1.4. Simulating the Design

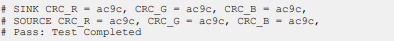

The DisplayPort Intel® FPGA IP design example testbench simulates a serial loopback design from a TX instance to an RX instance. An internal video pattern generator module drives the DisplayPort TX instance and the RX instance video output connects to CRC checkers in the testbench.

Figure 4. Design Simulation Flow

- Go to Synopsys simulator folder and select VCS.

- Run simulation script.

Source vcs_sim.sh

- The script performs Quartus TLG, compiles and run the testbench in the simulator.

- Analyze the result.