AN 875: Intel® Stratix® 10 E-Tile PCB Design Guidelines

ID

683262

Date

3/12/2019

Public

2.3.1. Design Target at 56 Gbps PAM4 Standard

Understanding the PAM4 standards is the key in the PAM4 PCB design flow. You must evaluate your channel loss budgets by using a loss estimate for each channel element in an end-to-end channel.

Below are the recommended channel losses for different standards:

50/56G PAM4 - Refer to each standard for the loss requirement:

- IEEE802.3bs

- IEEE802.3cd

- OIF CEI-56G-VSR

- OIF CEI-56G-MR

- OIF CEI-56G-LR

25/28G NRZ - Refer to each standard for the loss requirement:

- IEEE802.3bj

- IEEE802.3by

- OIF CEI-28G-VSR

- OIF CEI-28G-MR

- OIF CEI-28G-LR

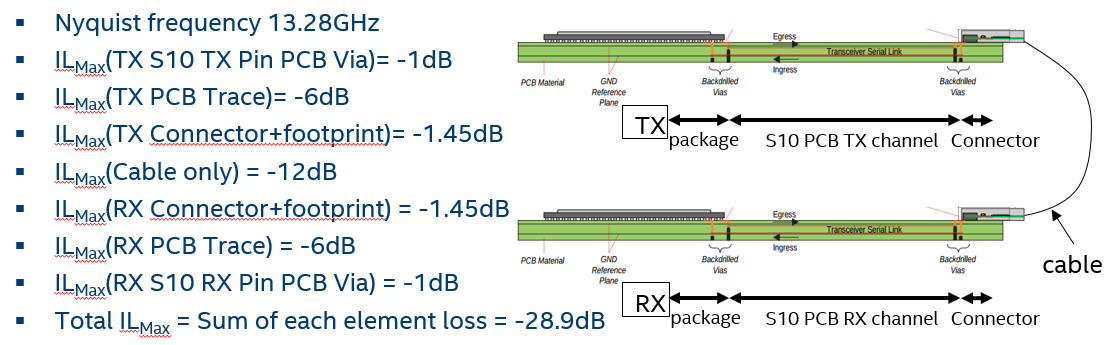

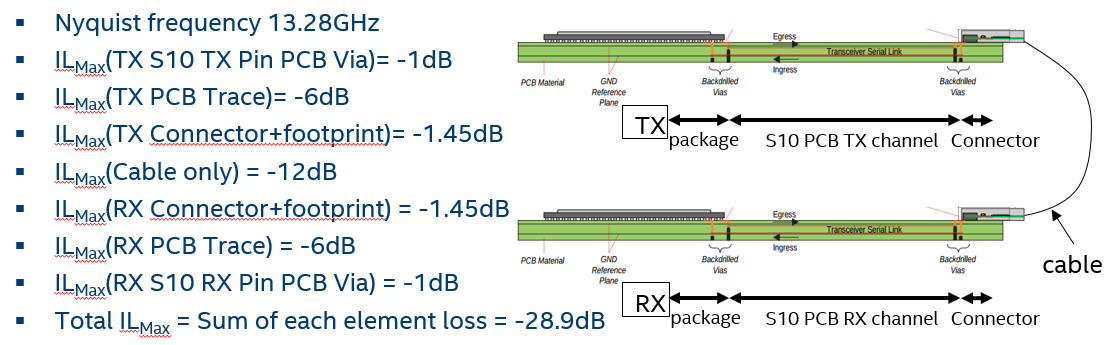

The following figure shows the channel insertion loss (IL) budget calculation for an end-to-end (TP0 to TP5) 200GBASE-CR4 channel, with the IL estimate at the Nyquist frequency for each channel element provided. Intel recommends that you estimate the minimum and maximum insertion loss allocations for each element of the channel (transmitter to receiver) carefully to meet the link standard (e.g. IEEE802.3cd).

Figure 6. Example of an end-to-end 200GBASE-CR4 Channel Loss Estimation

The boundaries of each element (i.e. connectors and cables) in the above example must be carefully defined.