AN 875: Intel® Stratix® 10 E-Tile PCB Design Guidelines

2.2. Intel® Stratix® 10 E-Tile Signaling - PAM4 vs. NRZ (PAM2)

The Intel® Stratix® 10 E-Tile enables both PAM4 and NRZ signaling.

PAM4 signaling uses four distinct voltage levels to encode two bits of data in every symbol, thereby doubling the bandwidth of the link without increasing the fundamental frequency.

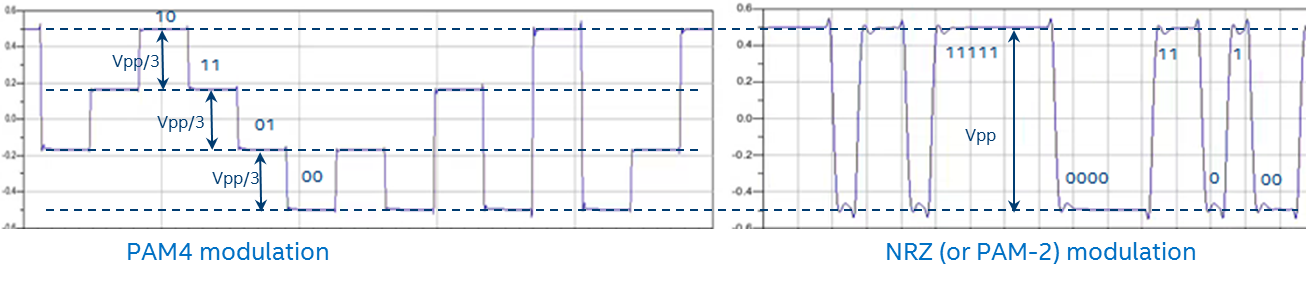

The following figure shows illustrations of PAM4 signaling and NRZ signaling.

In PAM4 mode, the noise margin is reduced compared to NRZ mode since in PAM4, the amplitude between adjacent signal levels is only one-third that of NRZ. This intrinsic loss compared to NRZ reduces the noise margin by approximately -9.5 dB. Therefore, noise margin is a critical consideration for the design of high-speed links using PAM4 signaling.

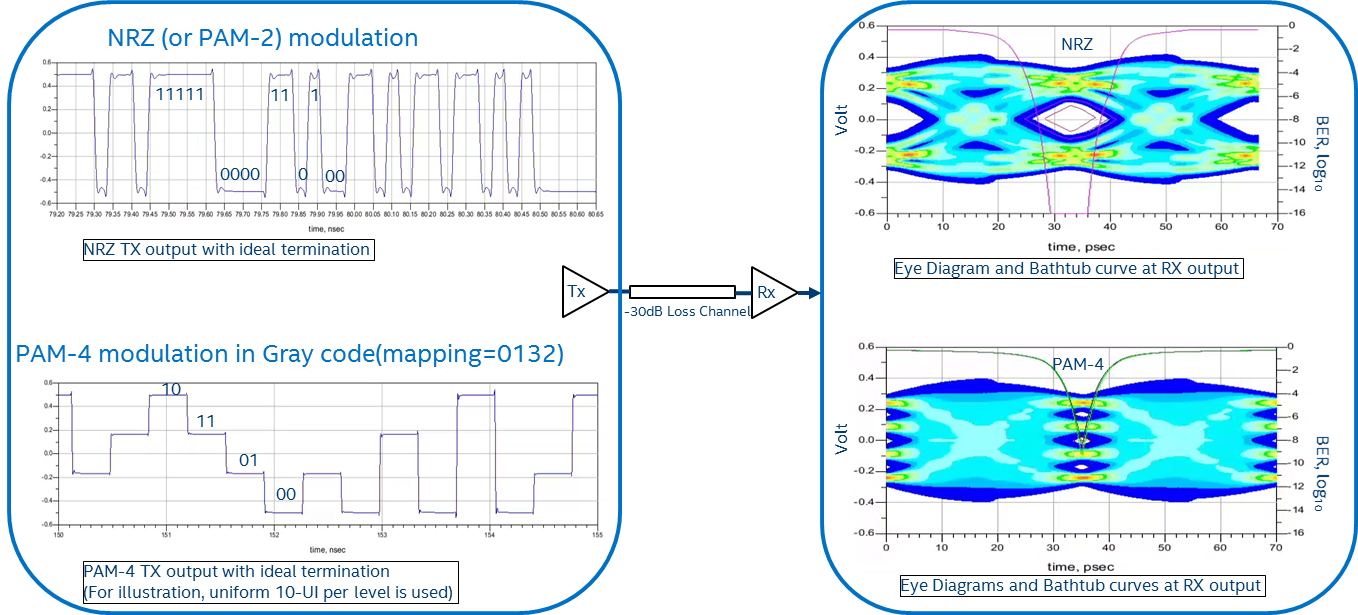

The following figure shows signal modulation examples in an Intel® Stratix® 10 E-Tile channel design for both NRZ and PAM4 signaling modes.

Due to the reduced noise margin in PAM4, the peak-to-peak eye opening is smaller than that in NRZ mode.