Intel® Quartus® Prime Pro Edition User Guide: Power Analysis and Optimization

A newer version of this document is available. Customers should click here to go to the newest version.

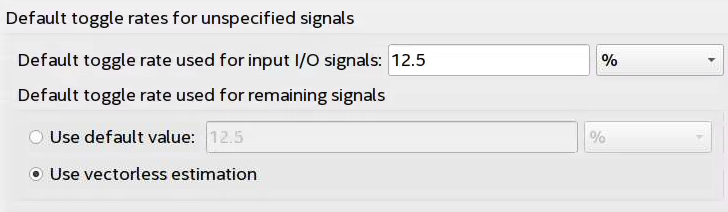

1.3.3. Specifying the Default Toggle Rate

You can specify the Default toggle rates for unspecified signals in your design for power analysis. The Power Analyzer uses the default toggle rate when no other method specifies the signal activity data.

You specify the toggle rate in absolute terms (transitions per second), or as a fraction of the clock rate in effect for each node. The toggle rate for a clock derives from the timing settings for the clock. For example, if the Power Analyzer specifies a clock with an fMAX constraint of 100 MHz and a default relative toggle rate of 20%, nodes in this clock domain transition in 20% of the clock periods, or 20 million transitions occur per second.

In some cases, the Power Analyzer cannot determine the clock domain for a node because the clock domain is ambiguous. For example, the Power Analyzer cannot determine a clock domain for a node unless you specify sufficient timing constraints for the clock domains. If the Power Analyzer cannot determine the clock domain for a node, the Power Analyzer substitutes and reports a toggle rate of zero.