Intel® High Level Synthesis Accelerator Functional Unit Design Example User Guide

3. Customizing the HLS AFU

To integrate an HLS component into an AFU, the AFU must provide the interfaces that your HLS component needs. You might need to update your host code as well.

At a high-level, to create an AFU from an HLS component, you must generate RTL for your component with the i++ command and then create a new UUID for the new AFU.

For details about how to create a UUID, see the Accelerator Functional Unit (AFU) Developer's Guide.

The steps that follow provide an example of how to replace the HLS component in the design example by replacing the fpVectorReduce_float component with the fpVectorReduce_ac_int component.

To replace the HLS component in the design example:

- Navigate to the qsys folder and create a new folder there called quartus_temp.

- Open the system with Platform Designer (from Intel® Quartus® Prime Pro Edition Version 17.1.1, provided with the Acceleration Stack) by running the following command from the qsys folder:

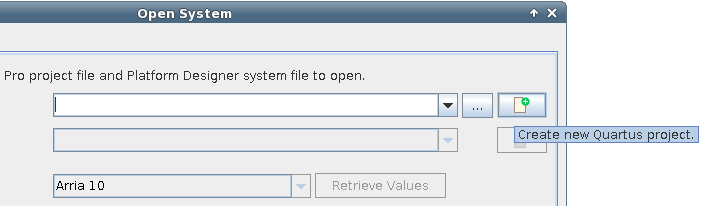

$ qsys-edit --search-path=../hls/test-fpga.prj/components/fpVectorReduce_float,\ ../hls/test-fpga.prj/components/fpVectorReduce_ac_int,$ hls_afu_container.qsys - To edit hls_afu_container.qsys, create an Intel® Quartus® Prime project by clicking Create New Quartus Project.

Figure 5. New Quartus Project

- Create a quartus_temp_prj project in the quartus_temp folder.

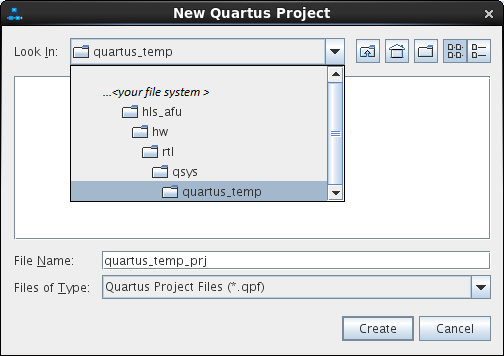

- Click Open on the Open System window.

Figure 6. Open System

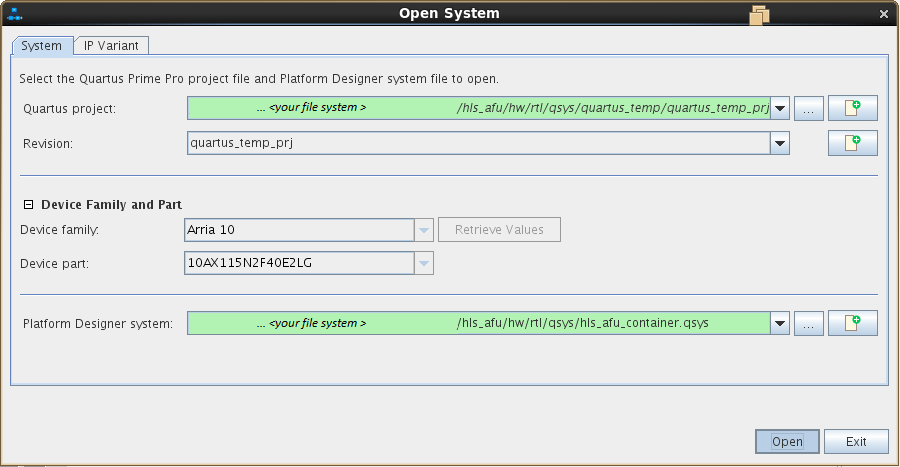

- Optional: If you have a custom HLS component that has a new UUID for your component, enter the UUID it in the afu_id_avmm_slave component parameters.

Enter the UUID as follows:

- In the AFU_ID_H field, enter the upper 64 bits of the UUID.

- In the AFU_ID_L field, enter the lower 64 bits of the UUID.

Figure 7. UUID

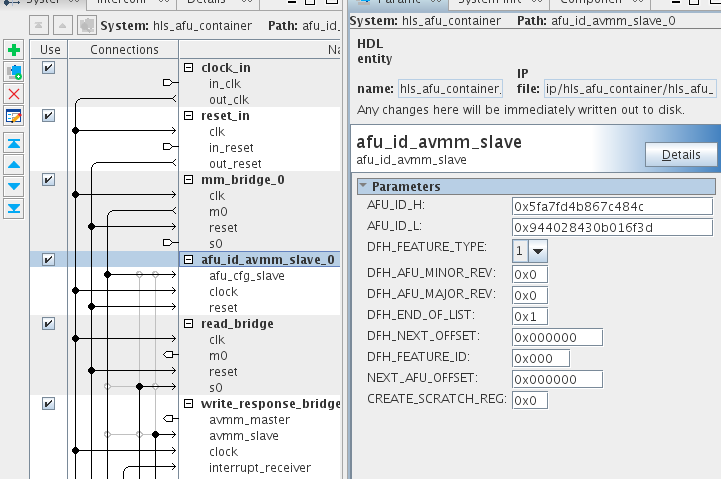

- Remove the fpVectorReduce_float component by right-clicking it and clicking Remove.

Figure 8. Remove Component

- In the Delete IP Variant dialog box, click No so that Platform Designer does not delete the fpVectorReduce_float IP file.

- Search for the fpVectorReduce_ac_int component in IP Catalog. Double-click the component to add it to the system.

Figure 9. Add Component

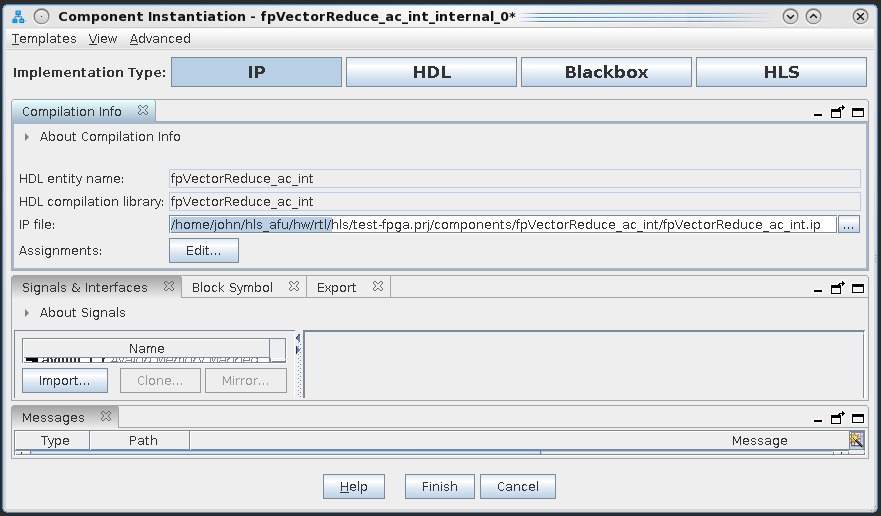

- In the Component Instantiation window, convert the absolute path for the IP file information to a relative path.

To convert the path to a relative path, edit the location of the IP file information to delete all the text preceding the hls folder (including the leading "/" character) and replace it with ".." (two periods).

Having a relative path here gives the .qsys file a relative path to your .ip file, so you can move your AFU project safely to a different file system.

Figure 10. Absolute Path Before Deleting Text Figure 11. Relative Path After Deleting Text

Figure 11. Relative Path After Deleting Text

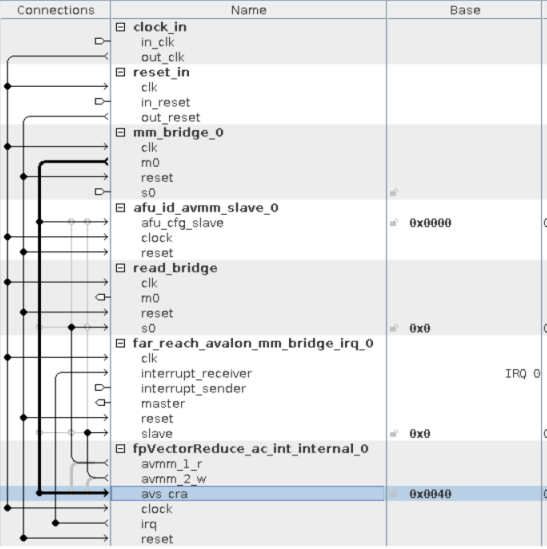

- Connect the new HLS component. In this case, the new component is the fpVectorReduce_ac_int component.

Make sure that you set the base address of your component Avalon-MM slave to 0x0040, so that the HLS component and AFU ID slave can share the same memory space, and the host application can access both.Figure 12. Set Base Address

- Click Validate System Integrity to update the Platform Designer system. A message appears at the bottom of the Platform Designer window indicating success.

- Save the system and exit Platform Designer.

Click Yes if you are asked to generate the changes.

- Configure your AFU by modifying the Acceleration Stack configuration files hls_afu/filelist.txt and hls_afu/hls_afu.json.

For examples of these files, see Acceleration Stack Configuration Files.

- Modify the host application to include the Avalon-MM slave register map that is produced by HLS.

- Copy the hls_afu/hw/rtl/hls/test-fpga.prj/components/fpVectorReduce_ac_int/fpVectorReduce_ac_int_csr.h header file to the host application project in hls_afu/sw/src.

- In hls_afu_host.c, include fpVectorReduce_ac_int_csr.h instead of fpVectorReduce_float_csr.h. Also replace the references to fpVectorReduce_float registers with references to fpVectorReduce_ac_int registers.

After you have customized the HLS AFU: