Intel® High Level Synthesis Accelerator Functional Unit Design Example User Guide

ID

683025

Date

7/19/2019

Public

2.1. HLS AFU Design Example Software Requirements

2.2. Compiling and Simulating the HLS Component with the i++ Command

2.3. Generating a Platform Designer Container for the HLS Component

2.4. Generating the ASE Testbench

2.5. Running the ASE Testbench

2.6. Compiling the AF Bitstream

2.7. Loading AF Bitstream and Running the Host Application

5.1. Platform Designer Opens with an Error

5.2. The design unit was not found Error When Running the make sim Command

5.3. Verilog HDL Compilation Errors

5.4. Compilation Errors During ASE Testbench Generation

5.5. Incorrect Output During Simulation

5.6. AF Bitstream Compilation Fails

5.7. Verilog Files Not Found Errors

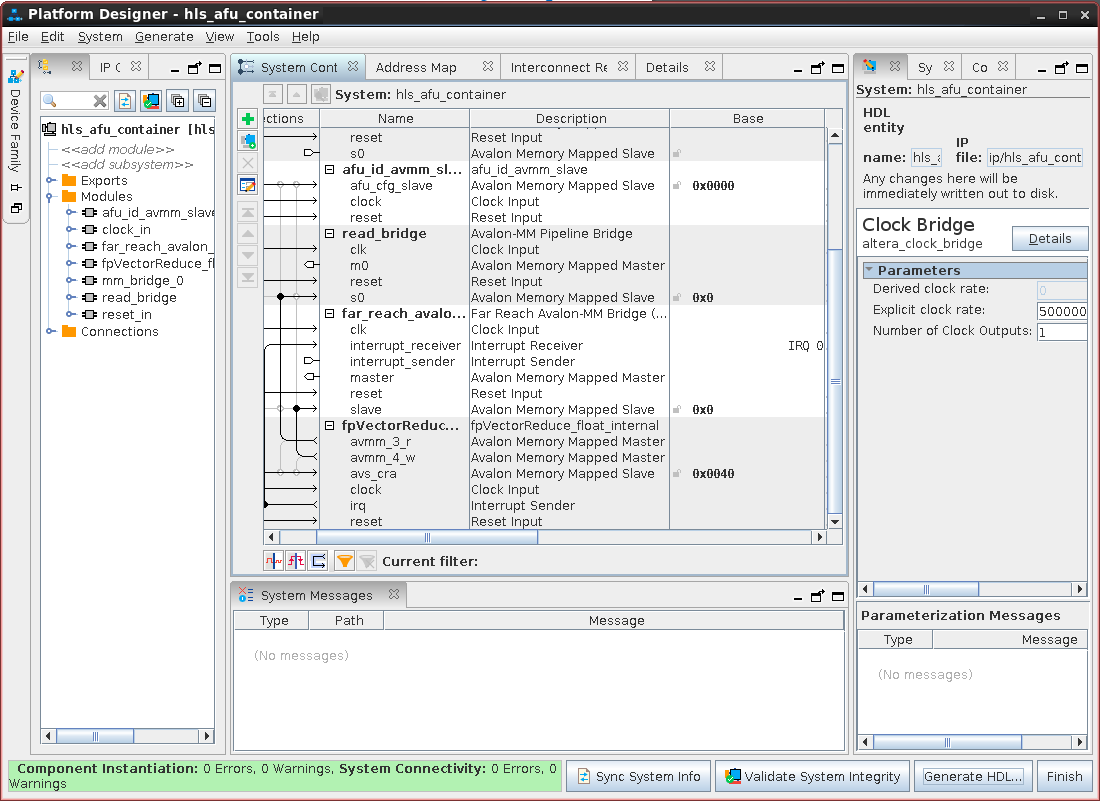

2.3. Generating a Platform Designer Container for the HLS Component

Use Platform Designer to integrate the HLS component into an AFU with the predesigned hardware interfaces available in the Acceleration Stack, and verify that all sources are linked correctly.

- You might need to set the environment variable values required by the Acceleration Stack. To set the variables, run the following command:

$ source /home/<username>/inteldevstack/init_env.sh - Navigate to the qsys folder and open the system using Platform Designer.

$ qsys-edit hls_afu_container.qsysYou can use a .ipx file to point to your IP files. In the design example, the hls_afu_container.ipx file points to where the HLS compiler-generated RTL is expected to be.

If you have other files in other locations that you need to include in your Platform Designer system, update the filelist.txt file with the paths to those files.

- In the Open System dialog box, select None for the Quartus project dropdown.

Ensure the Device part is 10AX115N2F40E2LG, which matches the FPGA on the Intel PAC with Intel® Arria® 10 GX device.If you want to modify the Platform Designer system, associate it to a temporary Intel® Quartus® Prime Pro Edition project.

- Click Open.

Figure 2. Open System Dialog box

- To reload the system and ensure that all search paths are correct, click Validate System Integrity at the bottom of the Platform Designer window.

- After Validate System Integrity successfully completes, click Close.

- Exit Platform Designer.

- Save the Platform Designer system.

- Click Yes to generate the HDL. Ignore any warnings.