3.5. GTS DisplayPort PHY Dual Simplex Mode IP Generation Flow

For designs with supported IP targeting Agilex™ 5 FPGAs only, you can create and view dual simplex logical assignments according to your channel arrangement. After defining dual simplex groups in the DS Assignment Editor, you run the HSSI Dual Simplex IP Generation stage of the Compiler to generate the dual simplex IP for synthesis. To use DS Assignment Editor to assign DS groups and run HSSI Dual Simplex IP Generation, follow these steps:

To use DS Assignment Editor to assign DS groups and save the dual simplex assignments, follow these steps:

- Open a Quartus® Prime Pro Edition project that targets the Agilex™ 5 device and includes a Platform Designer system with HSSI IP supporting dual simplex mode.

- Choose which Simplex TX and RX IPs to pair based on shared physical channels to form a dual simplex group.

- Click in the Quartus® Prime Pro Edition software. The DS Assignment Editor opens listing all the supported dual simplex IP in your design in the IP List and any existing DS assignments under DS Groups. In this example, the windows lists the generated 4-lane DP RX and DP TX and inside the DS tool as shown in the following figure.

Note: The DS Assignment Editor only displays the DS supported simplex IPs.Figure 16. DS Assignment Editor Before Creating DS Groups

- When your DS assignments are complete, click the Save Assignments to save the DS assignments to the .qsf for application during subsequent compilation stages. When you save the DS assignments, they are added automatically to the project .qsf file as shown in following figure.

Figure 17. DS Assignments in the Project QSF File

- In the Compilation Dashboard, click HSSI Dual Simplex IP Generation to generate the dual simplex IP.

Figure 18. HSSI Dual Simplex IP Generation Stage in Compilation Dashboard

Note: HSSI Dual Simplex IP Generation is present in Compilation Dashboard only when targeting Agilex™ 5 FPGAs. For more information about dual simplex mode, refer to GTS Transceiver Dual-Simplex Interfaces User Guide. - After running the Dual Simplex (DS) assignments, Quartus automatically includes the DS PHY IP core in your project. You can confirm this by finding a new .qip file in your Quartus project file set.

Figure 19. Dual Simplex IP Project Navigator

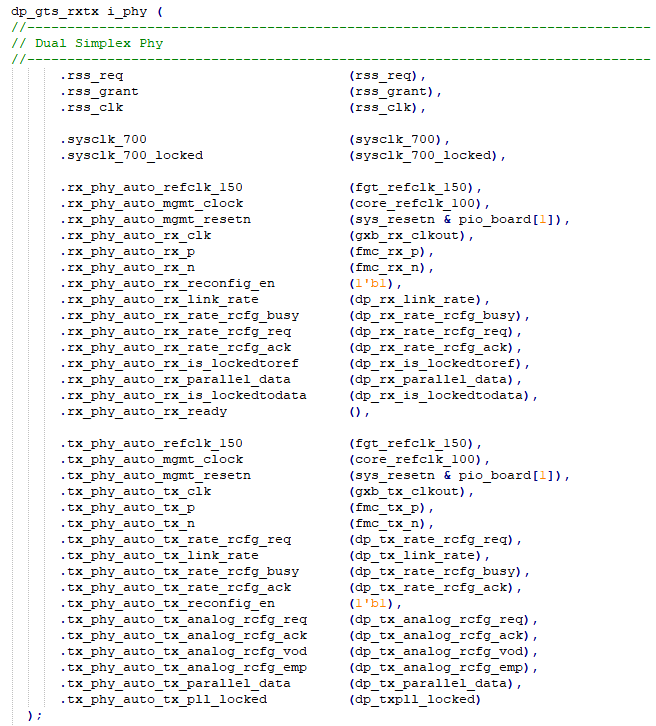

You must manually instantiate the DS PHY IP module when creating a new design. However, if you use ED generation, the tool automatically instantiates the DS PHY core for you as part of the generation process. The DS tool automatically saves output products in the Quartus project folder. For example, in the DisplayPort example, the IP core is saved in <project_dir>/quartus/dp_gts_rxtx.

The DS tool generates an example instantiation file with three distinct sections.- Reset Sequencer Interface: Common RSS interface

- RX PHY Interface: As defined by RX Simplex PHY

- TX PHY Interface: As defined by TX Simplex PHY

Figure 20. Dual Simplex PHY Instantiation File The Dual Simplex PHY appears in the hierarchy similarly to a Duplex PHY, as shown below. The distinction between them lies in the instantiation method.Figure 21. Duplex Simplex PHY

The Dual Simplex PHY appears in the hierarchy similarly to a Duplex PHY, as shown below. The distinction between them lies in the instantiation method.Figure 21. Duplex Simplex PHY