10.2. Reset Sequence Simulation

Reset sequence simulation verifies that persona functions start correctly after PR has completed. It can be done in the context of the whole design or as a block level simulation of just the persona. This simulation requires the post-synthesis gate-level PR simulation model of the persona. During the time when a PR operation occurs, you drive the pr_activate signal to set unknown (X) values into all registers inside the persona. After PR, the registers require to be explicitly reset to a known state.

The testbench sequence to run this simulation consists of the following:

- Assert the pr_activate signal.

- After completing PR, deassert the pr_activate signal.

- Reset the persona.

The simulation steps are as follows:

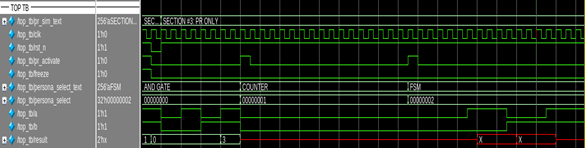

- Section reset occurs over two cycles to reset the persona to the default AND gate persona and reset the persona to a known state to ensure proper initial functionality.

- Simulation transitions to Section #2: PR, then reset.

- The persona transition sequence occurs. However, during this PR transition, the freeze signal does not assert. As a result, the output is undefined (as X) during this time until the reset is asserted to reset the output and the persona to a known state. This undefined output is a feature of the post-synthesis gate-level PR simulation model to output an undefined value during PR transitions.

Figure 14. Reset Sequence Simulation Waveform: Persona Registers Reset to a Known State

- Section Reset occurs again over two cycles to ensure the correct initial functionality. The simulation proceeds through the AND gate persona as expected.

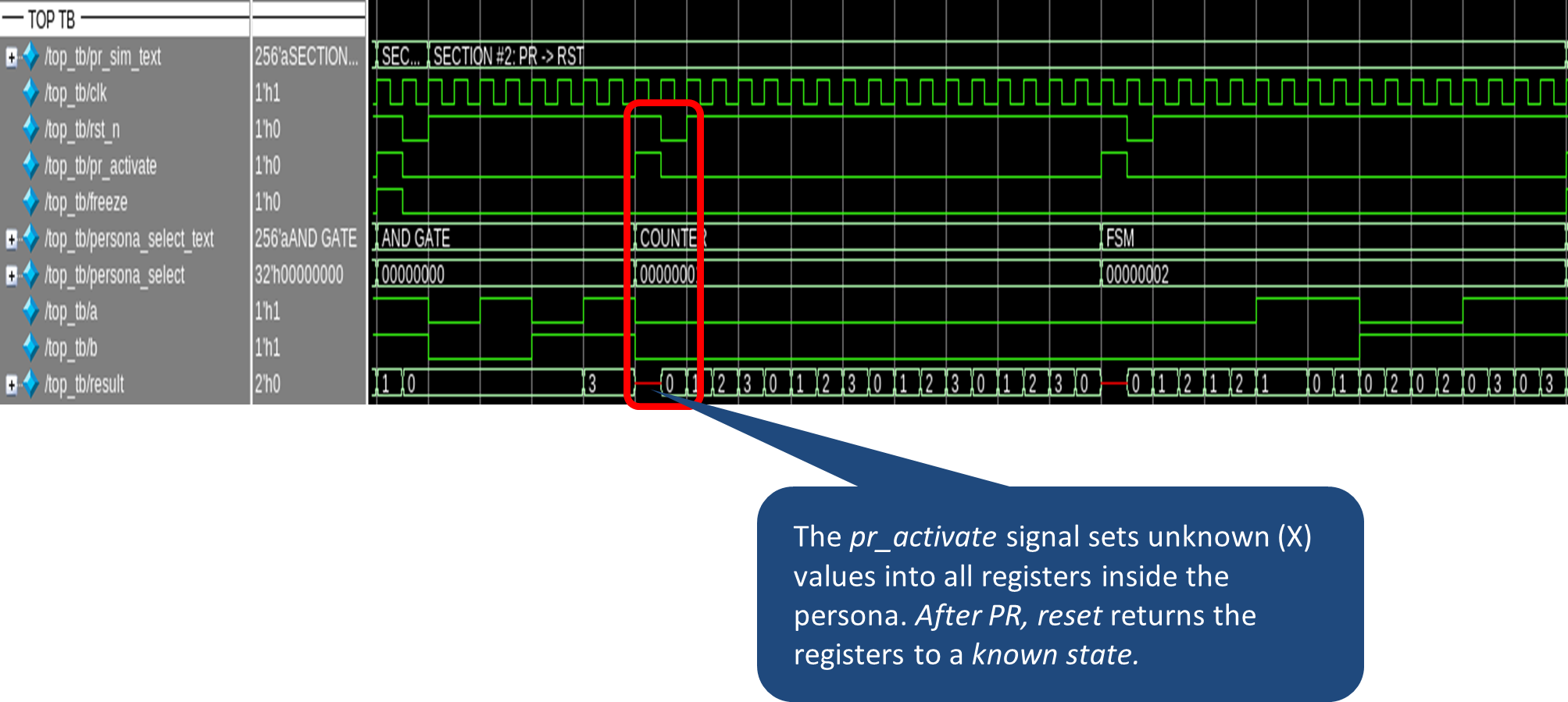

- Simulation transitions to Section #3: PR Only.

- Once the PR transition occurs and completes the transition to the counter persona, the output remains undefined. This is a result of not applying the reset to registers within the persona to reset the registers to a known state. This feature of the generated post-synthesis gate-level PR simulation model allows the output to remain an unknown (X) value until entering the known reset state.

- The undefined output continues throughout the counter persona, through the PR transition to the FSM persona, and through the FSM persona.

Figure 15. Reset Sequence Simulation Waveform: Persona Registers Do Not Reset to a Known State