8. Partial Reconfiguration Simulation Reference Design Files

The reference design files required for this tutorial are available in the Intel® FPGA Partial Reconfiguration Design Flow GitHub repository at https://github.com/intel/fpga-partial-reconfig.

To access the tutorial design:

- Go the GitHub repository at https://github.com/intel/fpga-partial-reconfig.

- On the repository page, click .

- Unzip the fpga-partial-reconfig-master.zip file.

- Navigate to the subfolder for your FPGA device:

- Agilex™ 5: tutorials/agilex5_pcie_devkit_pr_sim

- Agilex™ 7: tutorials/agilex7_pcie_devkit_pr_sim

- Arria® 10: tutorials/a10_pcie_devkit_pr_sim

- Stratix® 10: tutorials/s10_pcie_devkit_pr_sim

- The pr folder contains the files that you need to follow this tutorial.

- The pr_sim folder contains the complete set of files that you create using this application note.

| File Name | Description |

|---|---|

| top.sv |

Top-level file containing the flat implementation of the design. This file instantiates the pr_wrapper module. |

| pr_wrapper.sv |

Wrapper file for instantiating personas in the PR region. Default persona: AND gate. |

| and_gate.sv |

Persona Implementation: Synchronized AND gate with active low reset. Outputs the result of inputs ANDed together. |

| counter.sv |

Persona Implementation: Counter with active low reset. Outputs the top two MSBs of the counter. |

| fsm.sv |

Persona Implementation: FSM with active low reset. |

| File Name | Description |

|---|---|

| top_tb.sv |

Testbench file containing the simulation logic and the instantiation of top_sim module. The file also instantiates:

The top_sim module is the minimum requirement for the simulation. The personas are included to demonstrate the differences between using the gate-level PR simulation model versus the RTL for the personas. |

| top_sim.sv |

Top-level file for the simulation. This file instantiates the pr_sim_wrapper module. |

| pr_sim_wrapper.sv |

Wrapper file for instantiating the following items:

The file also includes the define ALTERA_ENABLE_PR_MODEL definition that directs the compiler to create and use the PR simulation register model for each register within a persona. |

| freeze_logic_controller.sv |

Control logic to freeze the PR region output while the PR transition is occurring. It allows the output to be set to a known value when activated and prevents any output from a persona during a PR transition to propagate into static portion of design. |

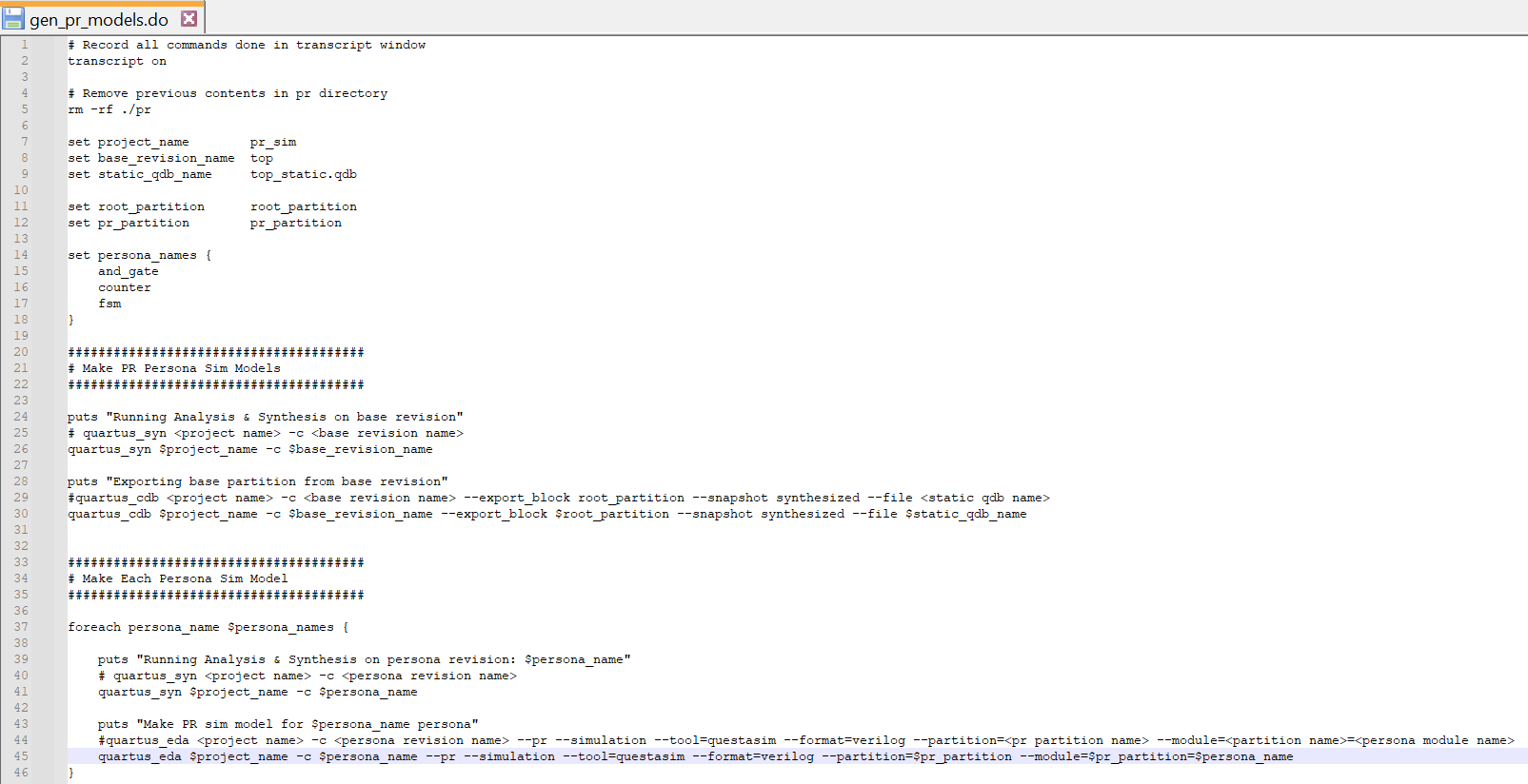

| gen_pr_models.do |

Script for generating gate-level PR simulation model for the personas. |

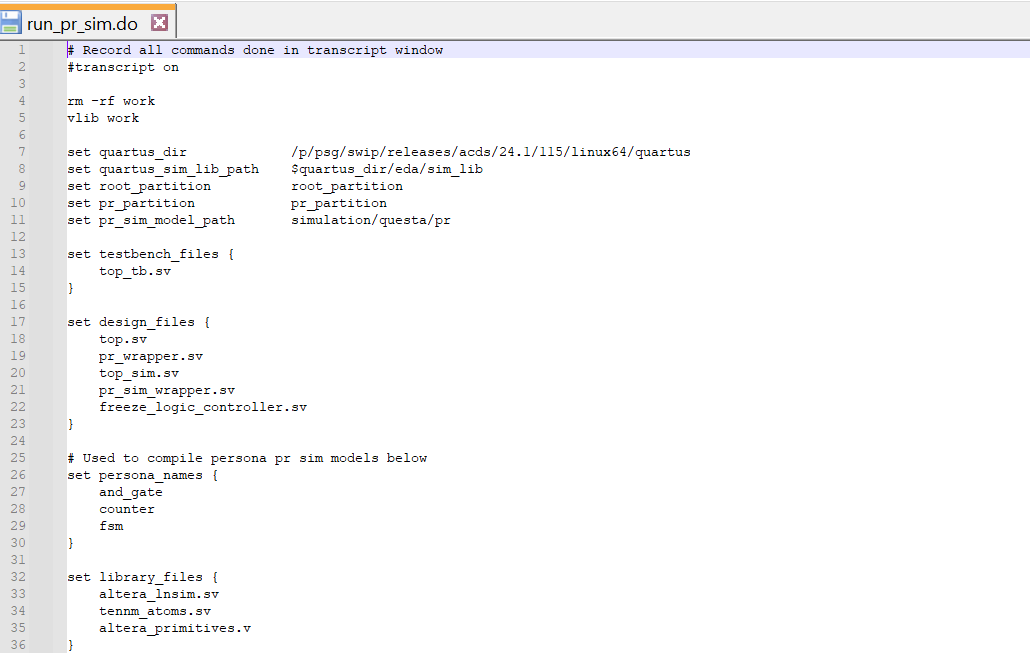

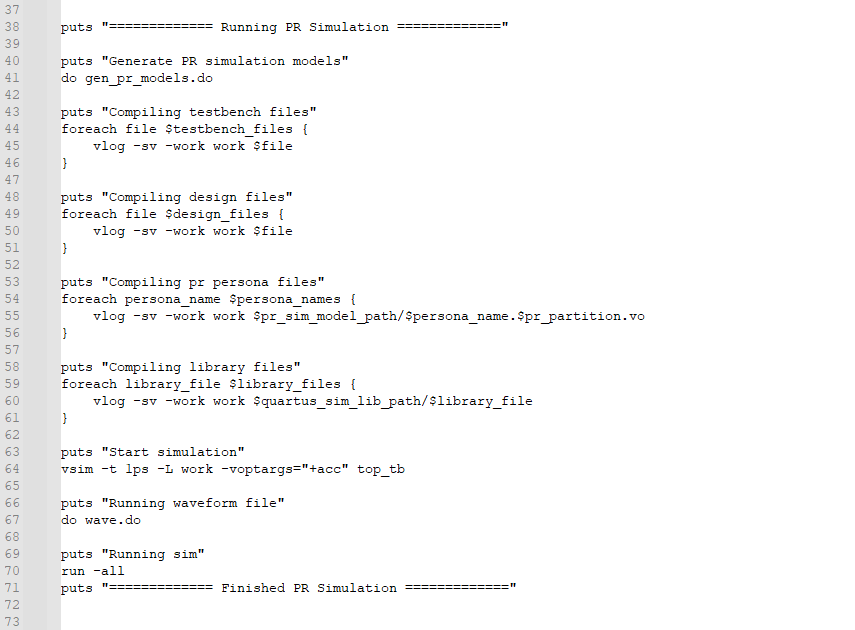

| run_pr_sim.do |

Script for generating gate-level PR simulation model for the personas and running the simulation. |

| run_pr_sim_only.do |

Script for running simulation (skips gate-level PR simulation model generation for the personas). |