7. Partial Reconfiguration Simulation Reference Design Overview

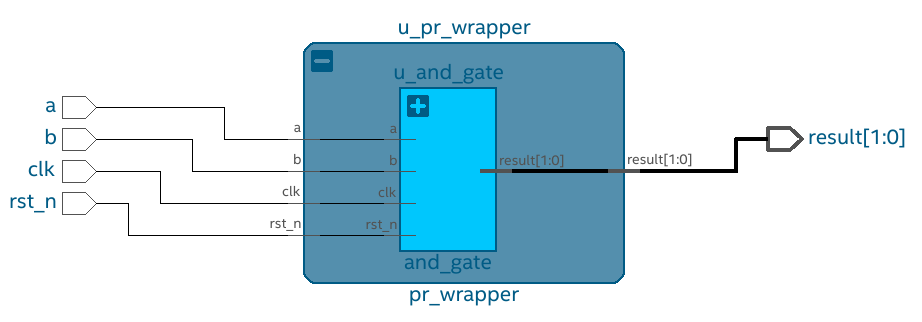

The reference design illustrates RTL and partial reconfiguration (PR) simulations in the Questa simulation software. It implements three PR personas inside a PR region. You can swap out the persona in the FPGA by using the partial reconfiguration process.

The personas in the reference design are as follows

- An AND gate

- A counter

- A finite state machine (FSM)

The PR Simulation Wrapper is the main component of the simulation design. It contains instantiations of the gate-level PR simulation model of each persona, PR input and output multiplexers, and freeze logic controller module.

Simulation only signals PR Activate, Persona Select and Freeze do not pass through the Top Simulation Module, but rather pass directly from the Testbench to the PR Simulation Wrapper. This technique is required because the testbench and simulation wrapper are not synthesizable, while the RTL top-level modules and personas are synthesizable in a real design scenario. The Testbench controls the signals as they pass through to the PR Simulation Wrapper directly using a relative path.

You can use the PR output MUX to output unknown values (X), when PR is active, to verify that unknown values exiting the PR region do not propagate into the static region. The unknown (X) outputs of the PR persona allow you to verify your freeze strategy.

You can trigger the PR simulation register model to show unknown (X) value in all registers of the persona. This technique allows you to validate the reset sequence by showing that all registers return to a known state after PR completes and you apply reset.

The RTL simulation as well as the PR simulation (with gate-level PR simulation model of the personas), both use the same Testbench and PR Simulation Wrapper.