AN 923: Routing Intel® Stratix® 10 HPS Peripherals to FPGA Fabric

ID

683838

Date

10/12/2020

Public

1.2.1. Prerequisites

1.2.2. Getting Started

1.2.3. Generating the Initial HDL in Platform Designer

1.2.4. Modifying Top Level File

1.2.5. Adding Pin Assignments for SPIM0

1.2.6. Hardware Programming File Compilation and Generation

1.2.7. Building U-Boot

1.2.8. Preparing QSPI Image

1.2.9. Building Linux

1.2.10. Building Yocto Rootfs

1.2.11. Building spidev Test Program

1.2.12. Creating SD Card Image

1.2.13. Booting the Board

1.2.14. Testing the SPIM0

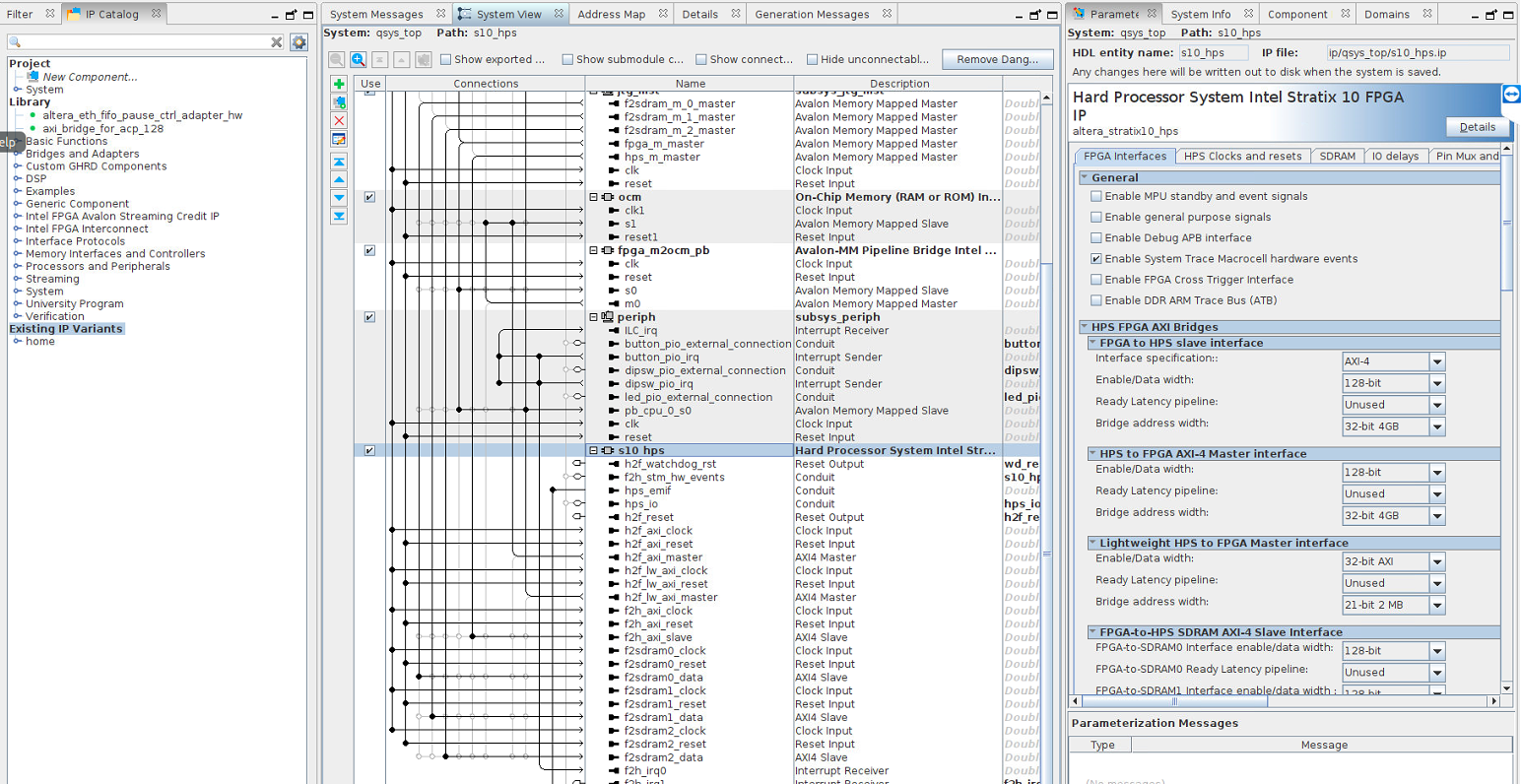

1.2.3. Generating the Initial HDL in Platform Designer

- In the Quartus Prime Pro Edition navigation bar, select Tools > Platform Designer .

- In the Platform Designer window, select File > Open > qsys_top.qsys .

- In the System View tab, double click on s10_hps to open the HPS Parameters window.

Figure 2. System Contents Window

- Go to Pin Mux and Peripherals > Advanced > Advanced FPGA placement and select the Route to FPGA box for SPIM0 to Yes, then click on Apply Selections.

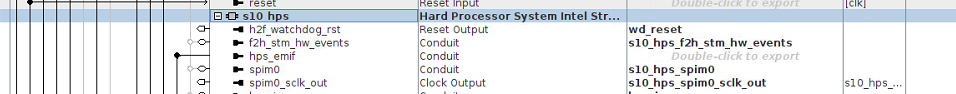

- Double click in the Export column to export the s10_hps.spim0 conduit.

- Double click in the Export column to export the s10_hps.spim0_sclk_out conduit.

Figure 3. Exported Signals

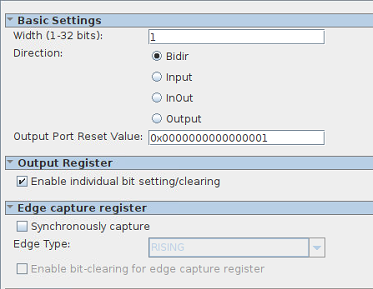

- Add a new GPIO soft IP to use as SPI chip select.

- Add a new component of type PIO (Parallel I/O) Intel FPGA IP, name it spi_cs_pio and configure it as follows:

- Width: 1

- Direction: bidir

- Enable individual bit setting/clearing: yes

- Output Port Reset Value: 0x0000000000000001

Figure 4. PIO Settings

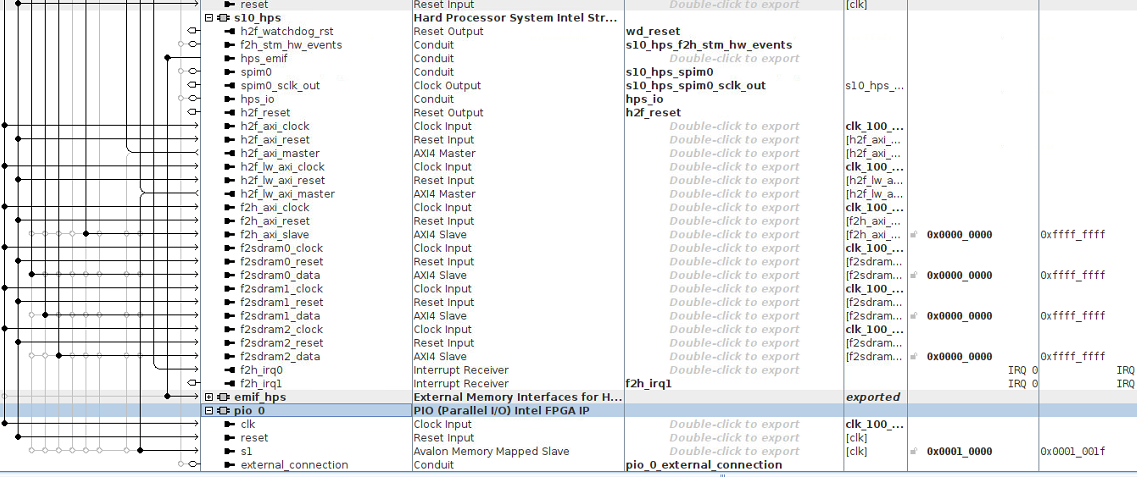

- Change the base address of spi_cs_pio.s1 to 0x0001_0000 to avoid conflicts with other IPs.

- Connect the spi_cs_pio as follows:

clk: to clk_100.out_clk

reset: to rst_in.out_reset

s1: to s10_hps.h2f_lw_axi_master

Double click on the spi_cs_pio.external connection to export it and create the conduit spi_cs_pio.spi_cs_pio_external_connection_export.

Figure 5. PIO Connections

- Go to Generate > Show Instantiation Template, and save the template in a file, so you have the new signal names for qsys_top.

- Click on the Generate button to generate the system.