A newer version of this document is available. Customers should click here to go to the newest version.

2.1. Installing and Licensing Intel® FPGA IP Cores

2.2. IP Catalog and Parameter Editor

2.3. Specifying the IP Core Parameters and Options

2.4. Simulating Intel® FPGA IP Cores

2.5. Simulating the IP with the RTL Simulator

2.6. Simulating the Turbo IP with the C-Model

2.7. Simulating the Turbo IP with MATLAB

2.3. Specifying the IP Core Parameters and Options

Quickly configure Intel® FPGA IP cores in the Intel® Quartus® Prime parameter editor. Double-click any component in the IP Catalog to launch the parameter editor. The parameter editor allows you to define a custom variation of the IP core. The parameter editor generates the IP variation synthesis and optional simulation files, and adds the .ip file representing the variation to your project automatically.

Follow these steps to locate, instantiate, and customize an IP core in the parameter editor:

- Create or open an Intel® Quartus® Prime project (.qpf) to contain the instantiated IP variation.

- In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize. To locate a specific component, type some or all of the component’s name in the IP Catalog search box. The New IP Variation window appears.

- Specify a top-level name for your custom IP variation. Do not include spaces in IP variation names or paths. The parameter editor saves the IP variation settings in a file named <your_ip> .ip. Click OK. The parameter editor appears.

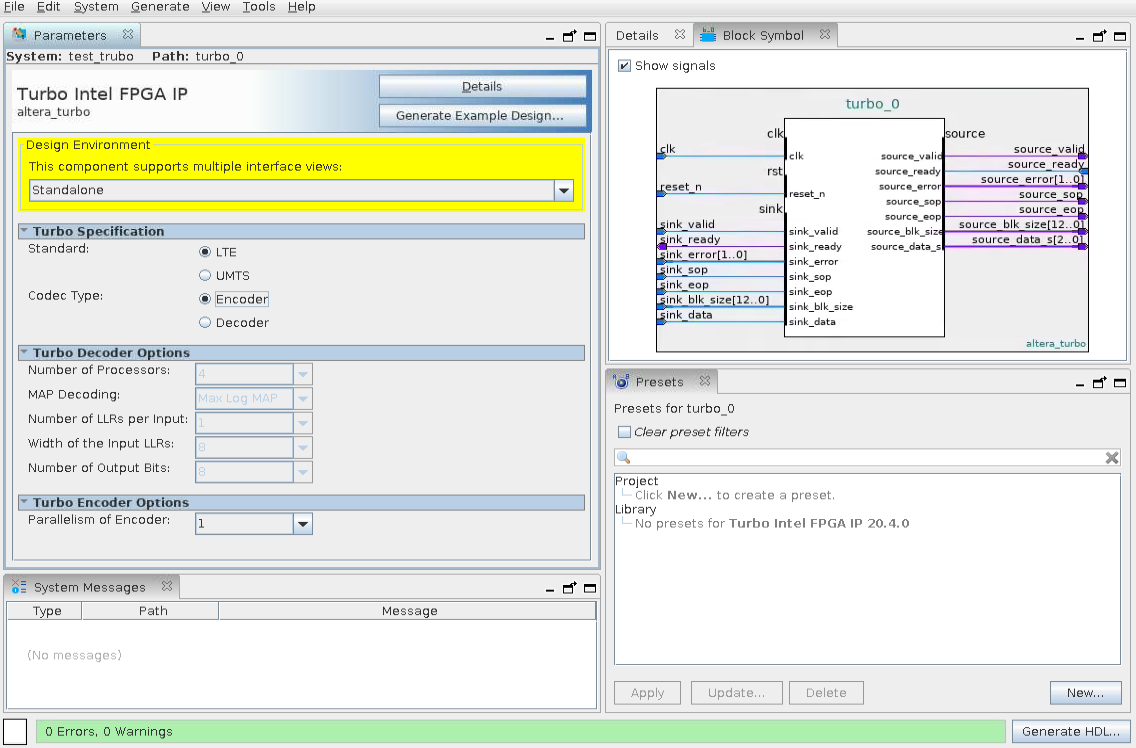

Figure 4. IP Parameter Editor ( Intel® Quartus® Prime Pro Edition)

- Set the parameter values in the parameter editor and view the block diagram for the component. The System Messages tab at the bottom displays any errors in IP parameters:

- Optionally, select preset parameter values if provided for your IP core. Presets specify initial parameter values for specific applications.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

Note: Refer to your IP core user guide for information about specific IP core parameters. - Click Generate HDL. The Generation dialog box appears.

- Specify output file generation options, and then click Generate. The synthesis and simulation files generate according to your specifications.

- To generate a simulation testbench, click Generate > Generate Testbench System. Specify testbench generation options, and then click Generate.

- To generate an HDL instantiation template that you can copy and paste into your text editor, click Generate > Show Instantiation Template.

- Click Finish. Click Yes if prompted to add files representing the IP variation to your project.

- After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

Note: Some IP cores generate different HDL implementations according to the IP core parameters. The underlying RTL of these IP cores contains a unique hash code that prevents module name collisions between different variations of the IP core. This unique code remains consistent, given the same IP settings and software version during IP generation. This unique code can change if you edit the IP core's parameters or upgrade the IP core version. To avoid dependency on these unique codes in your simulation environment, refer to Generating a Combined Simulator Setup Script.