Intel® Hyperflex™ Architecture High-Performance Design Handbook

A newer version of this document is available. Customers should click here to go to the newest version.

2.4.2.9.2. Use Simple Dual-Port Memories

When migrating a design to the Intel® Hyperflex™ architecture, consider whether your original design contains a dual-port memory that uses different clocks on each port, and the maximum frequency you plan to operate the memory. If your design is actually using the same clock on both write ports, restructure it using two simple dual-clock memories.

The advantage of this method is that the simple dual-port blocks support frequencies up to 1 GHz. The disadvantage is the doubling of the number of memory blocks required to implement your memory.

Dual Port, Dual Clock Memory Implementation

module true_dual_port_ram_dual_clock #(parameter DATA_WIDTH=8, parameter ADDR_WIDTH=6) ( input [(DATA_WIDTH-1):0] data_a, data_b, input [(ADDR_WIDTH-1):0] addr_a, addr_b, input we_a, we_b, clk_a, clk_b, output reg [(DATA_WIDTH-1):0] q_a, q_b ); // Declare the RAM variable reg [DATA_WIDTH-1:0] ram[2**ADDR_WIDTH-1:0]; always @ (posedge clk_a) begin // Port A if (we_a) begin ram[addr_a] <= data_a; q_a <= data_a; end else begin q_a <= ram[addr_a]; end end always @ (posedge clk_b) begin // Port B if (we_b) begin ram[addr_b] <= data_b; q_b <= data_b; end else begin q_b <= ram[addr_b]; end end endmodule

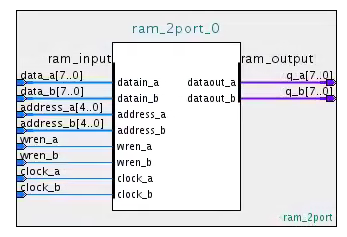

Synchronizing dual-port memory that uses different write clocks can be difficult. Ensure that both ports do not simultaneously write to a given address. In many designs the dual-port memory often performs a write operation on one of the ports, followed by two read operations using both ports (1W2R). You can model this behavior by using two simple dual-port memories. In simple dual-port memories, a write operation always writes in both memories, while a read operation is port dependent.