3.3.1. Output Data Width

For a decimation filter, the gain at the output of the filter is:

G = RM N

Therefore, the data width at the output stage for if full resolution is:

B out = B in + Nlog2(RM)

where Bin is the input data width.

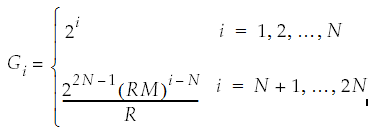

For an interpolation filter, the gain at each filter stage is:

Hence the required data width at the ith stage is:

W i = [B in + log2(G i )]

and the data width at the output stage is:

B out = [B in + Nlog2(RM) - log2(R)]

where B in is the input data width.

When the differential delay is one, the bit width at each integrator stage is increased by one to ensure stability.

For more information about these calculations, refer to Hogenauer, Eugene. An Economical Class of Digital Filters For Decimation and Interpolation, IEEE Transactions on Acoustics, Speech and Signal Processing, Vol. ASSP-29, pp. 155-162, April 1981.