3. CIC Intel® FPGA IP Functional Description

You can select either a decimation or interpolation CIC filter. A decimation CIC filter comprises a cascade of integrators (integrator), followed by a down sampling block (decimator) and a cascade of differentiators (called the differentiator or comb section). Similarly an interpolation CIC filter comprises a cascade of differentiators, followed by an up sampling block (interpolator) and a cascade of integrators.

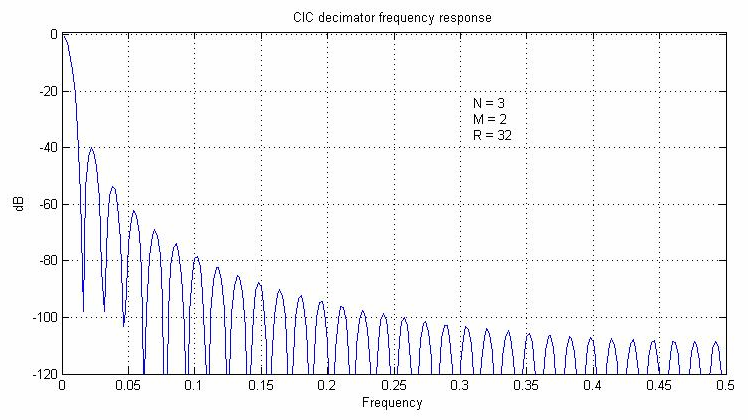

In a CIC filter, both the integrator and comb sections have the same number of integrators and differentiators. Each pairing of integrator and differentiator is a stage. The number of stages (N) has a direct effect on the frequency response of a CIC filter. You determine the response of the filter by configuring:

- The number of stages N

- The rate change factor R

- The number of delays in the differentiators (differential delay) M. Generally, set the differential delay to 1 or 2.

Figure 6. Three-stage CIC Decimation Filter Frequency ResponseCIC decimation filter with N = 3, M = 2 and R = 32