Quartus® Prime Pro Edition User Guide: Design Constraints

A newer version of this document is available. Customers should click here to go to the newest version.

1.1.4. Specifying Timing Constraints

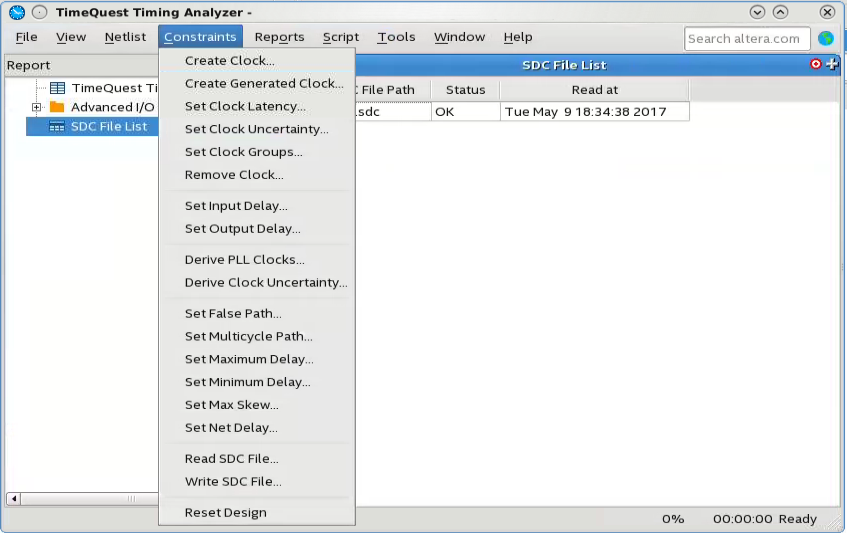

You can specify timing constraints in the Timing Analyzer GUI, which automatically generates an .sdc based on your inputs. Click the Constraints menu in the Timing Analyzer to specify timing constraints that you can apply to your project.

Alternatively, you can create an initial .sdc with provided .sdc file templates, or manually in any text editor and then add the .sdc to the project.

In addition, generation of Intel FPGA IP or Platform Designer systems may also automatically generate and add to your project .sdc constraints.

When you specify a constraint in the GUI, the dialog box displays the equivalent SDC command syntax.

Create Clock Dialog Box

Individual timing assignments override project-wide requirements.

- To avoid reporting incorrect or irrelevant timing violations, you can assign timing exceptions to nodes and paths.

- The Timing Analyzer supports point-to-point timing constraints, wildcards to identify specific nodes when making constraints, and assignment groups to make individual constraints to groups of nodes.

Refer to the following Related Information: